#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

UMI

| - |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

#### Order Number 2136851

High yield and reliable sorting networks for VLSI and WSI implementations

Liang, Sheng-Chiech, Ph.D. The University of Arizona, 1991

# HIGH YIELD AND RELIABLE SORTING NETWORKS FOR VLSI AND WSI IMPLEMENTATIONS

by

Sheng-Chiech Liang

A Dissertation Submitted to the Faculty of the

#### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

In Partial Fulfillment of the Requirements

For the Degree of

DOCTOR OF PHILOSOPHY

WITH MAJOR IN ELECTRICAL ENGINEERING

In the Graduate College

THE UNIVERSITY OF ARIZONA

1991

## THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE

| As members of the Final Examination Committee                                                        | ee, we certify that we have read  |

|------------------------------------------------------------------------------------------------------|-----------------------------------|

| the dissertation prepared by Sheng-Chie                                                              | ech Liang                         |

| entitled HIGH YIELD AND RELIABLE SORTING                                                             | NETWORKS FOR VLSI AND WSI         |

| IMPLEMENTATIONS                                                                                      |                                   |

|                                                                                                      |                                   |

|                                                                                                      |                                   |

|                                                                                                      |                                   |

|                                                                                                      |                                   |

| and recommend that it be accepted as fulfil                                                          | ling the dissertation requirement |

| for the Degree of <u>Doctor of Philosophy</u>                                                        | •                                 |

| The South Hold                                                                                       |                                   |

| Dr. Fredrick J. Hill                                                                                 | April 26, 1991 Date               |

| 1 20 //                                                                                              | Annil 26 1001                     |

| Dr. Sy-Yen/Kuo                                                                                       | April 26, 1991  Date              |

| 10                                                                                                   | April 26, 1991                    |

| Dr. Ahmed Louri                                                                                      | Date                              |

|                                                                                                      |                                   |

|                                                                                                      | Date                              |

|                                                                                                      | Date                              |

| Final approval and acceptance of this disse candidate's submission of the final copy of College.     |                                   |

| I hereby certify that I have read this dissidirection and recommend that it be accepted requirement. |                                   |

| Dissertation pirector (Dr. Sy-Yen Kuo)                                                               | <u>April 26, 1991</u><br>Date     |

#### STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under the rules of the library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgement of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the head of the major department or the Dean of the Graduate College when in his or her judgement the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the author.

SIGNED: Shenz-Chark Lang

#### **ACKNOWLEDGMENTS**

The author wishes to express his deepest gratitude to his dissertation advisor, Dr. Sy-Yen Kuo, for his support, encouragement, and insightful guidance throughout this dissertation work.

The author would also like to thank Dr. Fredrick J. Hill and Dr. Ahmed Louri for their advice and time, and all his colleagues in the Fault Tolerant Computing Group for their friendship and intellectual stimulation. The support by the National Science Foundation under Grant MIP-89-08648 is also gratefully acknowledged.

The author wishes to thank his parents and family whose love and support made it possible to complete this dissertation. Last but not least, he would like to express his appreciation to his wife, Huei-Chuan, for her continual encouragement, understanding, faith, and patience throughout his Ph.D. studies.

## TABLE OF CONTENTS

| LIST OF FIGURES                                             | 8  |

|-------------------------------------------------------------|----|

| LIST OF TABLES                                              | 10 |

| ABSTRACT                                                    | 11 |

| 1. INTRODUCTION                                             | 13 |

| 1.1. Objective                                              | 13 |

| 1.2. Overview of the Fault-Tolerant Systolic Sorting Arrays | 16 |

| 1.3. Overview of the Defect-Tolerant WSI Sorting Networks   | 16 |

| 1.4. Overview of the Trapezoid Sort                         | 17 |

| 1.5. Overview of the Kth Smallest Value Extraction          | 18 |

| 1.6. Overview of the Modified Odd-Even Merge Procedure      | 18 |

| 2. THE FAULT-TOLERANT SYSTOLIC SORTING ARRAYS               | 19 |

| 2.1 Introduction                                            | 19 |

| 2.2 Array Architecture and Cell Realization                 | 22 |

| 2.3. Properties of the Sorting Array                        | 26 |

| 2.4. Fault Tolerance                                        | 34 |

| 2.5. Design of Totally Self-Checking Checkers               | 42 |

| 2.6 Evaluation and Discussion                               | 47 |

| 2.7. Summary                                   |         | 52  |

|------------------------------------------------|---------|-----|

| 3. THE DEFECT-TOLERANT WSI SORTING N           | ETWORKS | 54  |

| 3.1. Introduction                              |         | 54  |

| 3.2. Hierarchical Modular Sorting Networks     |         | 56  |

| 3.3. Optimal Decomposition                     |         | 61  |

| 3.4. Easily Reconfigurable Equivalent Networks |         | 68  |

| 3.5. Defect Tolerance                          |         | 72  |

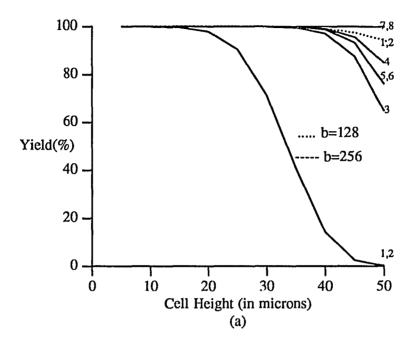

| 3.6. Yield Analysis                            |         | 79  |

| 3.7. Summary                                   |         | 84  |

| 4. THE TRAPEZOID SORT                          |         | 86  |

| 4.1. Introduction                              |         | 86  |

| 4.2. The Trapezoid Sort                        |         | 87  |

| 4.3. Analysis and Time Complexity              |         | 90  |

| 4.4. Summary                                   |         | 98  |

| 5. THE Kth SMALLEST VALUE EXTRACTION           |         | 99  |

| 5.1. Introduction                              |         | 99  |

| 5.2. Properties of the Trapezoid Sort          |         | 100 |

| 5.3. Finding the Kth Smallest Element          |         | 109 |

| 5.4. Summary                                   |         | 121 |

| 6. THE MODIFIED ODD-EVEN MERGE PROCE           | EDURE   | 122 |

| 6.1. Introduction                              |         | 122 |

| 6.2. The Modified Odd-Even Merge               |         | 123 |

|    | 6.3. Analysis                          | 135 |

|----|----------------------------------------|-----|

|    | 6.4. Summary                           | 137 |

| 7. | CONCLUSIONS                            | 138 |

|    | 7.1. Summary and Discussions           | 138 |

|    | 7.2. Suggested Future Research         | 141 |

|    | APPENDIX A: NETWORK TRANSFORMATION     | 142 |

|    | APPENDIX B: PERMUTATION TRANSFORMATION | 144 |

|    | REFERENCES                             | 147 |

## LIST OF FIGURES

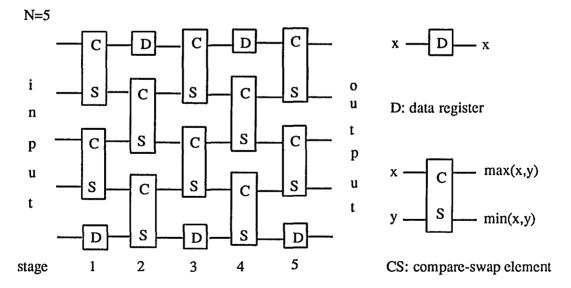

| 2.1. Odd-even transposition sort: comparator-network representation     | 23 |

|-------------------------------------------------------------------------|----|

| 2.2. Odd-even transposition sort: word-level structure.                 | 23 |

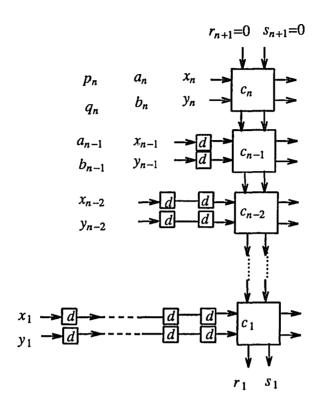

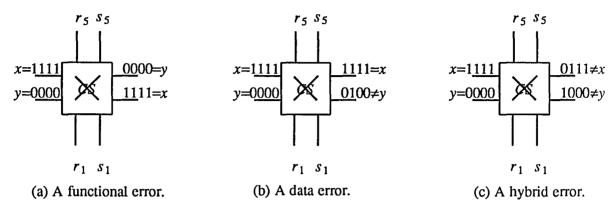

| 2.3. Structure of a CS element and the matrix of data registers.        | 25 |

| 2.4. Structure of a compare-swap cell and its logical functions.        | 26 |

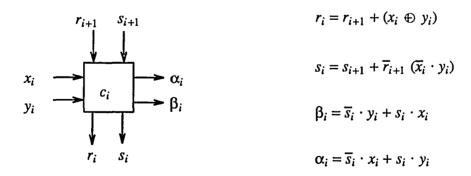

| 2.5. Example errors                                                     | 28 |

| 2.6. A comparator-network representation of a faulty element at stage k | 32 |

| 2.7. On-line fault diagnosis procedure.                                 | 38 |

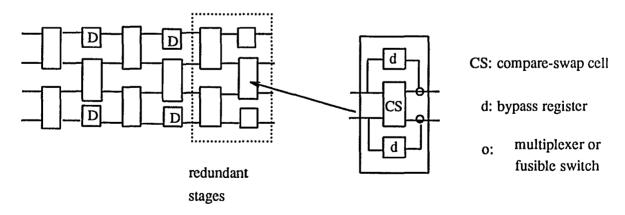

| 2.8. Compare-swap element with bypass registers and switches.           | 41 |

| 2.9. System degradation scheme.                                         | 41 |

| 2.10. Totally self-checking data error detector.                        | 43 |

| 2.11. A complete fault-tolerant sorting array with N+3 stages           | 48 |

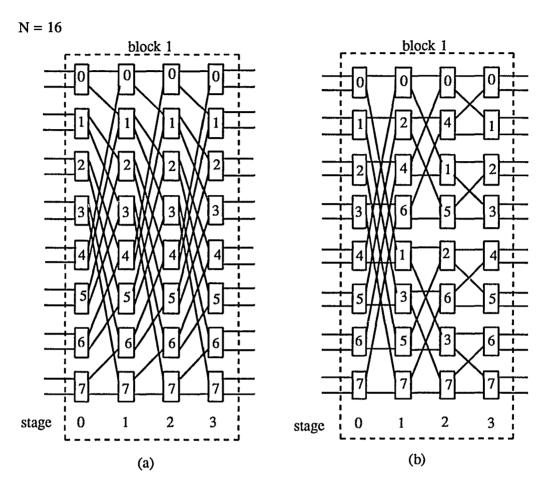

| 3.1. Hierarchical sorter.                                               | 57 |

| 3.2. The balanced sorter.                                               | 60 |

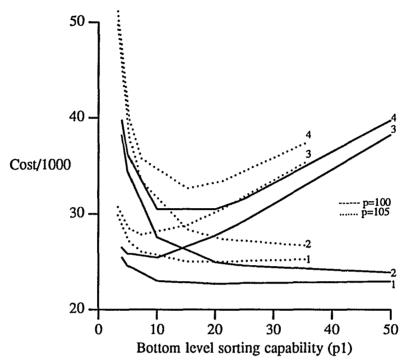

| 3.3. Cost $C$ vs. $p_1$ for cases 1, 2, 3 and 4 with $p = 100$ and 105  | 67 |

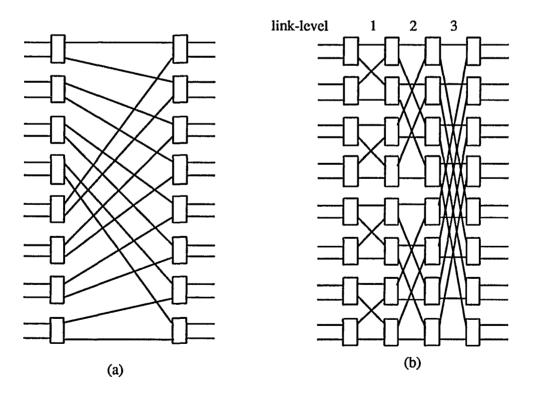

| 3.4. Omega network and modified data manipulator.                       | 69 |

| 3.5. Shuffle permutation $\sigma$ and Banyan permutation $r$ .          | 70 |

| 3.6. Balanced permutation $\tau$ and permutation $\psi$                 | 71 |

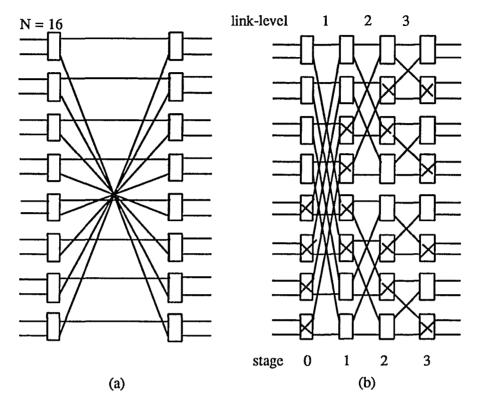

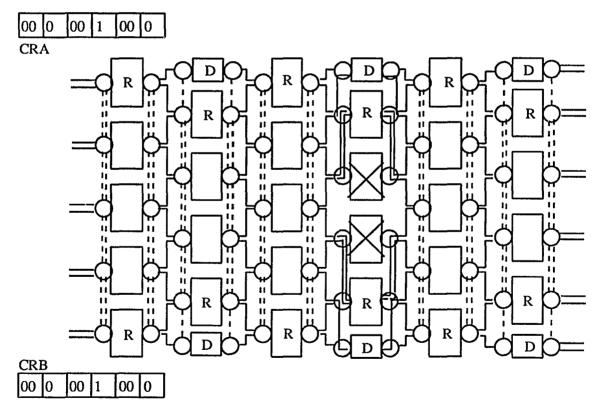

| 3.7. Example reconfigurable structure of the odd-even transposition sorter | 72  |

|----------------------------------------------------------------------------|-----|

| 3.8. Output functions of a switching element in the top-level.             | 73  |

| 3.9. On-line reconfigurable odd-even transposition sorter                  | 74  |

| 3.10. Example reconfiguration in the middle-level.                         | 76  |

| 3.11. Butterfly interconnections with and without wrap-around wires        | 78  |

| 3.12. Example yield analysis.                                              | 83  |

| 4.1. An example of snake-like row major indexing scheme.                   | 88  |

| 4.2. The trapezoid sort algorithm.                                         | 89  |

| 4.3. An example output of step 2 with $n=7$ .                              | 90  |

| 4.4. The maximum number of dirty rows = 3 for $Q_{7\times7}$ .             | 93  |

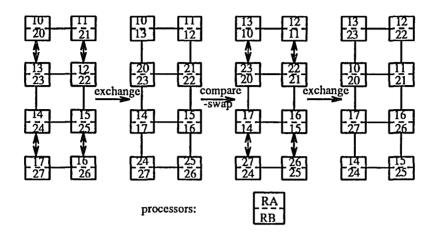

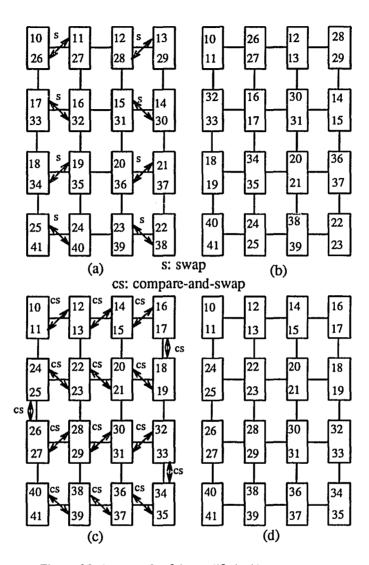

| 6.1. A compare-and-swap step in the column-sort.                           | 124 |

| 6.2. A modified compare-and-swap step in the column-sort.                  | 126 |

| 6.3. An example of the modified odd-even merge.                            | 127 |

| 6.4. An example $8\times8$ $L_A$ .                                         | 128 |

| 6.5. Merge sort procedure.                                                 | 131 |

| 6.6. Modified odd-even merge procedure.                                    | 133 |

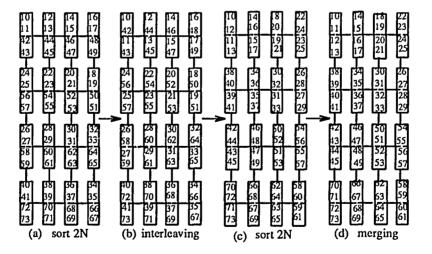

| 6.7. An example of sorting 4N inputs.                                      | 134 |

## LIST OF TABLES

| 2.1. | Reservation table.                                               | 39         |

|------|------------------------------------------------------------------|------------|

| 2.2. | Overhead ratios.                                                 | 51         |

| 3.1. | The amount of redundancy for each case.                          | 63         |

| 3.2. | The cost $C$ with $p=20$ .                                       | 64         |

| 3.3. | The cost $C$ with $p=100$ .                                      | 64         |

| 3.4. | The cost $C$ with $p=105$ .                                      | 65         |

| 3.5. | The cost $C$ with $p=200$ .                                      | 65         |

| 3.6. | Regions covered by CRA and CRB.                                  | <b>7</b> 4 |

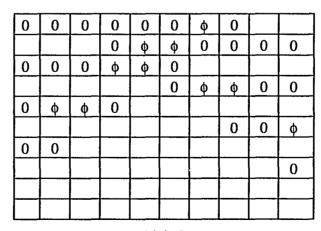

| 5.1. | An example output of step 2 with $n=7$ .                         | 101        |

| 5.2. | The maximum number of dirty rows = 3 for $Q_{7\times7}$ .        | 104        |

| 5.3. | The relationship between $r_{p+k}$ and $k$ .                     | 114        |

| 5.4. | The distribution of zeros in each row after the second row sort. | 115        |

#### **ABSTRACT**

In this dissertation, a novel approach to on-line error detection and correction for high throughput VLSI sorting arrays is presented first. Two-level pipelining is employed in the design which makes the proposed VLSI sorting array very efficient and suitable for real-time applications. In addition, all the checkers are designed as totally self-checking circuits such that the resulting sorting array is extremely reliable.

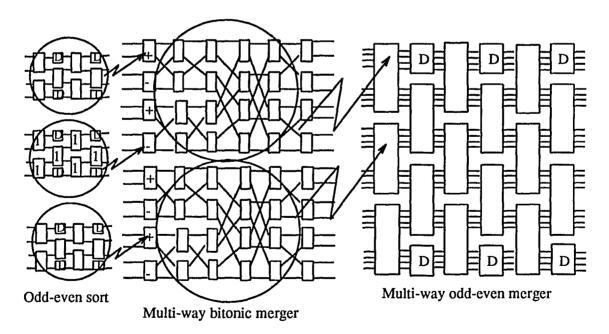

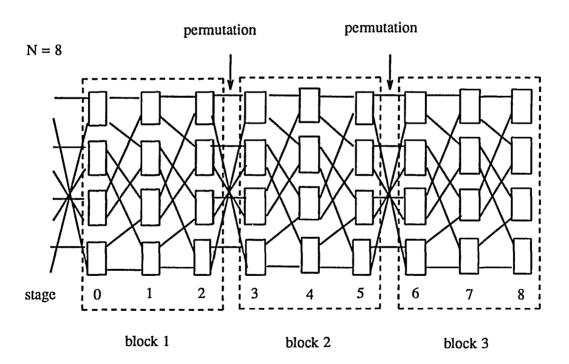

Next, in order to overcome the yield problem in WSI implementations a novel hierarchical modular sorting network is presented. This design is based on the tradeoffs in area and time between the odd-even transposition sort and the bitonic sort. More regularly structured equivalent sorting networks are introduced by replacing shuffle interconnections in the original sorting network with easily reconfigurable interconnections. Redundancy is provided at every level of the hierarchy. Hierarchical reconfiguration is implemented by replacing the defective cells with spare cells at the bottom level first, and goes to the next higher level. Yield analysis is performed to demonstrate the effectiveness of our approach.

Efficient implementation of parallel sorting algorithms for mesh-connected processor arrays are also considered in this dissertation. The *trapezoid sort* which has the properties of very simple control hardware and ease of implementation for mesh-connected processor arrays is developed. This algorithm is a combination of recursively sorting elements of two neighbor rows into opposite directions, sorting elements in each column, and a *cyclic shift* after the first row sort to rearrange the output order of each row. Its advantage is that the number of iterations is improved significantly compared with the existing parallel sorting algorithms on mesh-

connected processor arrays.

Based on this algorithm, an efficient method is proposed to find the median value of the input elements. The elements outside the boundary are excluded from the remaining sorting process to reduce the time complexity and the median value can be found without completely sorting the array. This method is then extended to finding the *k*th smallest element in the input array.

Finally, if the number of elements to be sorted is larger than N, the trapezoid sort algorithm can not be applied directly. Therefore, a modified odd-even merge procedure is presented to merge m sorted input sets. The modified odd-even merge procedure can sort two sets of data inputs concurrently by utilizing the idle processors and then merge them together. A speedup of  $O(log_2 m)$  over the previous merge-split method is achieved.

#### CHAPTER 1.

#### INTRODUCTION

#### 1.1. Objective

Many applications in real-time digital signal and image processing need a high performance and special purpose architecture for parallel sorting on a huge amount of input data [1,2,3]. Sorting arrays which consist of a number of identical processing elements with regular interconnections and high concurrency factors [4], such as the odd-even transposition sort [5], the bitonic sort [6], and the perfect shuffle sort [7], are good candidates for real-time applications. Use of these arrays has become attractive mainly due to the availability of VLSI and WSI technologies at a reasonable cost.

Studies by Kung [8] indicate that both regular cell structures and simple interconnections will dominate the cost in VLSI or WSI implementations. Also by considering the ratio (Aw/At) of the wiring space to the total area as a function of the number of inputs, Horiguchi [9, 10] showed that the Aw/At ratio is approximately one for the perfect shuffle sort or the bitonic sort and is a constant 0.1 for the mesh connected odd-even sort when the number of inputs N is large.

Therefore, although both the perfect shuffle sort and the bitonic sort use less sorting elements  $(O(N\log_2^2 N))$  than the odd-even transposition sort  $(O(N^2))$  [11], the wiring complexities of the first two sorters make them more costly to implement than the odd-even sort since, for

large N, the wiring space will dominate the silicon area. This is why the more regularly structured odd-even transposition sort is a better candidate for VLSI implementations than other parallel sorting algorithms.

In addition to the area-time performance, reliability, availability, and continuous operation are important in real-time applications [12, 13]. Also, the defect tolerance capability (yield), the capability of a system to survive from defects, is also very important in manufacturing. In order to increase the system reliability and availability, a highly reliable sorting array which can detect multiple errors and correct a single error for on-line applications is presented. Furthermore, due to the large area and the processing technology limitation, defects seems unavoidable in VLSI and WSI implementation. Therefore, the sorting array needs to have defect tolerance capabilities. In this dissertation, we also present a novel hierarchical modular sorting network (HMSN) which is based on the tradeoffs between the simple communication scheme of the odd-even transposition sort and the fast convergent speed of the bitonic sort. Spare sorting elements are incorporated in every level of the hierarchy so that it can survive from defects in an efficient way.

Moreover, parallel sorting algorithms for two-dimensional mesh-connected processor arrays also have been intensively studied in [14,15,16,17] and more recently, in [18,19,20,21,22]. These earlier efforts were adaptations of inherently parallel algorithms such as the odd-even merge sort and the bitonic sort to the mesh-connected array in an efficient manner such that the time complexity is O(n). However, these implementations spend most of the time in routing data to appropriate processors, and the complicated data movements in successive iterations result in complicated control structures and thus, offset the advantage of simple interconnections.

Recently, Sado and Igarashi [19], and Scherson and Sen [21] presented two similar parallel sorting algorithms independently, the parallel bubble sort and the shear sort, respectively, for two-dimensional SIMD model. These sorting algorithms are based upon a repeated application of the bubble-sort method [5] to the rows and columns of the array to be sorted. They are indeed two-dimensional sorting techniques and have the advantages that it is extremely simple to implement them in any of the two-dimensional computing models and their control complexity is reduced considerably due to their repetitive and nonrecursive nature. However, they have a drawback that  $\lceil \log_2 n \rceil + 1$  iterations are required to sort an  $n \times n$  input array.

In this dissertation, we present a new two-dimensional sorting algorithm, the  $trapezoid\ sort$ , which preserves the properties of simple control hardware and ease of implementation of the  $row-column\ sort$ , and the complexity is improved to  $\lceil \log_2 l \rceil + 1$  iterations with  $l \approx \sqrt{n}$ . This will algorithm can be used to find the kth smallest value of the inputs without the input sequence being completely sorted. Reduction on processing steps also means reduction in silicon area when the algorithm is implemented as a VLSI sorting network. However, the algorithms discussed above were designed to sort  $N = n \times n$  inputs only, where N is the number of processors in the mesh array. If the number of elements to be sorted is larger than N, they can not be applied directly. To overcome this, the method in [14,21] uses the mergesplit operation to replace the compare-interchange (or compare-and-swap in this paper) operation and  $O(m\log_2 m)T_N$  time complexity is required to sort mN inputs where  $T_N$  represents the time complexity to sort N inputs. Although that method is simple, it is not efficient. A novel  $modified\ odd-even\ merge\ method\ is\ proposed\ in\ this\ dissertation\ which can merge\ m\ sorted\ sets\ in\ <math>O(\frac{m}{2}\cdot\log_2 m)n$  time complexity. The other advantage of the proposed method is that it is quite simple and regular.

#### 1.2. Overview of the Fault-Tolerant Systolic Sorting Arrays

In chapter 2, a novel approach to on-line error detection and correction for high throughput VLSI sorting arrays is presented. The error model is defined at the sorting element level and errors generated are considered as functional errors if the outputs from a faulty sorting element are not ordered correctly and as data errors if the output data values were modified by the faulty sorting element. Functional errors are detected and corrected by exploiting inherent properties as well as discovered special properties of the sorting array. Coding techniques and an on-line fault diagnosis procedure are developed to locate data errors. All the checkers are designed to be totally self-checking and hence the sorting array is highly reliable. Two-level pipelining is employed in our design which makes it very efficient and suitable for real-time application. The hardware overhead is not significant for typical array sizes and the time penalty is only 3 clock cycles. The structure is very regular and therefore, is very attractive for VLSI implementation.

#### 1.3. Overview of the Defect-Tolerant WSI Sorting Networks

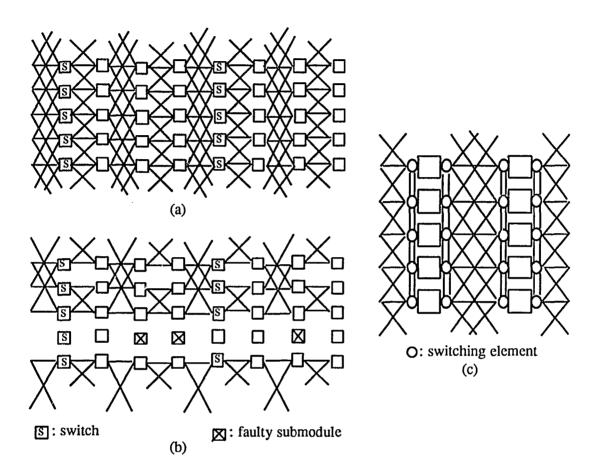

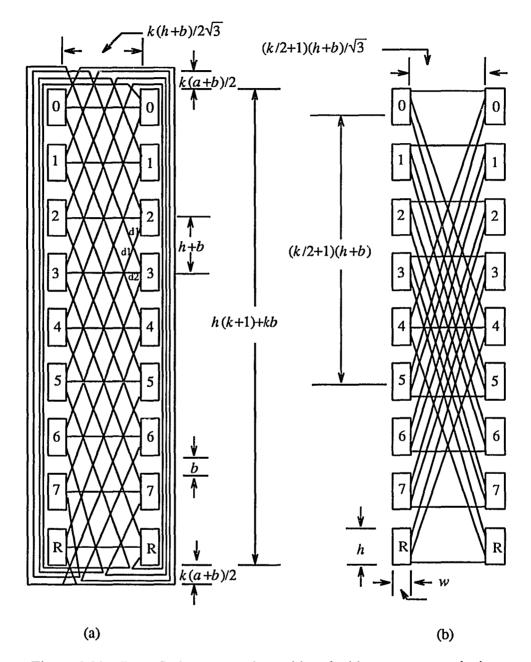

In order to overcome the yield problem in WSI, a novel hierarchical modular sorting network is presented in chapter 3. The design is based on the tradeoffs in area and time between the odd-even transposition sort and the bitonic sort. It uses less hardware than a single-level odd-even transposition sorter and reduces the wire complexity problem of the bitonic sorter in VLSI or WSI (wafer scale integration) implementation. The optimal number of levels in the hierarchy is analyzed and sorting capability of each level is derived to minimize the hardware complexity. More regularly structured equivalent sorting networks are introduced by replacing

shuffle interconnections in the original sorting network with easily reconfigurable interconnections. The hierarchical sorting network is very regular in structure after the equivalent network transformation and hence easier to include defect tolerance capability than any existing sorting network with the same time complexity. Redundancy is provided at every level of the hierarchy. Hierarchical reconfiguration is implemented by replacing the defective cells with spare cells at the bottom level first, and goes to the next higher level to perform reconfiguration if there is not enough redundancy at the current level. Yield analysis is performed to demonstrate the effectiveness of our approach.

#### 1.4. Overview of the Trapezoid Sort

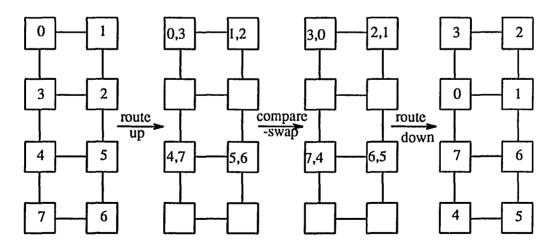

A parallel sorting algorithm, the *trapezoid sort*, for mesh-connected processor arrays is presented in chapter 4. Given a sequence of numbers mapped onto an  $n \times n$  array, the *trapezoid sort* will generate a sorted output sequence stored in the array in snake-like row major order. This algorithm is a combination of recursively sorting elements of two neighbor rows into opposite directions, sorting elements in each column, and a *cyclic shift* after the first row sort to rearrange the output order of each row. It preserves the properties of very simple control hardware and ease of implementation, and has the advantage that the number of iterations improved significantly from  $\lceil \log_2 n \rceil + 1$  to  $\lceil \log_2 l \rceil + 1$  with  $(l^2+l)/2 \le n < (l^2+3l+2)/2$  in comparison with the existing parallel sorting algorithms on mesh-connected processor arrays.

#### 1.5. Overview of the Kth Smallest Value Extraction

Properties of the *trapezoid sort* are derived in chapter 5. The maximum distance boundary of an element in an array to be sorted after the second iteration of the trapezoid sort from its position in the final sorted output array is determined first. An efficient method is also developed in chapter 5 to find the median value of the input elements by exploiting the property that the boundary distance will be reduced by half after each successive iteration. The elements outside the boundary are excluded from the remaining sorting process which reduces the complexity and the median value can be found without completely sorting the array. This method is then extended to find the *k*th smallest element in the input array.

#### 1.6. Overview of the Modified Odd-Even Merge Procedure

The row-column sort algorithms on mesh-connected processor arrays, such as the parallel bubble sort and the shear sort, have the properties of very simple control hardware and ease of implementation. However, these row-column sort algorithms are based on the odd-even transposition sort such that half of the processors are idle during each basic comparison-interchange step. In addition, they are designed to sort N inputs only, where N is the number of processors in the array. If the number of elements to be sorted is larger than N, the row-column sort algorithms can not be applied directly. Therefore, a modified odd-even merge procedure is presented in chapter 6 to sort two sets of data inputs concurrently by utilizing the idle processors and then merge them together. This procedure is further generalized to merge m sorted input sets (m>2) where each set can be initially sorted by any algorithm. A speedup of  $O(\log_2 m)$  over the previous merge-split method is achieved.

#### CHAPTER 2.

#### THE FAULT-TOLERANT SYSTOLIC SORTING ARRAYS

#### 2.1 Introduction

Many applications in real-time digital signal and image processing need a high performance and special purpose architecture for parallel sorting on a huge amount of input data. Sorting arrays which consist of a number of identical processing elements with regular interconnections and high concurrency factors [4], such as the odd-even transposition sort [5], the bitonic sort [6], and the perfect shuffle sort [7], are good candidates for real-time applications. Use of these arrays has become attractive mainly due to the availability of VLSI and WSI technologies at a reasonable cost. Studies by Kung [8] indicate that both regular cell structures and simple interconnections will dominate the cost in VLSI or WSI implementations. Also by considering the ratio (Aw/At) of the wiring space to the total area as a function of the number of inputs, Horiguchi [10] showed that the Aw/At ratio is approximately one for the perfect shuffle sort or the bitonic sort and is a constant 0.1 for the mesh connected odd-even sort when the number of inputs N is large. Therefore, although both the perfect shuffle sort and the bitonic sort use less sorting elements  $(O(N\log_2^2 N))$  than the odd-even transposition sort  $(O(N^2))$ , the wiring complexities of the first two sorters make them more costly to implement than the oddeven sort since, for large N, the wiring space will dominate the silicon area. This is why the more regularly structured odd-even transposition sort is a better candidate for VLSI implementation than other parallel sorting algorithms.

Reliability, availability, and continuous operation are also very important in real-time applications. On-line error detection is the first requirement to increase the reliability. In order to increase the system availability, off-line diagnosis after on-line error detection should be avoided and the system should be able to automate the recovery process. In this chapter, we present a highly reliable sorting array which can detect multiple errors and correct a single error for on-line applications. In addition, it is highly available. As a systolic sorting array based on the odd-even transposition sort, it has a regular structure and simple interconnection links. Both the regularity and the simplicity are preserved by the presented fault tolerance technique so that redundancy can be included into the system easily, either to enhance the system performance or to replace the faulty elements. Also, it can be reconfigured easily to tolerate the faulty sorting elements located by the on-line fault diagnosis procedure and can be degraded gracefully after redundancy is exhausted.

Recently, an algorithm-based fault-tolerant sorter was proposed in [23]. They developed an on-line error detection method for the systolic priority queue [24] by applying the time redundancy approach to the operation of sorting a sequence of N inputs serially. Since it is a serial sorter which uses N/2 sorting elements and 2N clock cycles to sort N inputs, it is not suitable for real-time applications. Therefore, its entire structure as well as the fault tolerance techniques are different from the proposed highly pipelined sorting array. Also, by comparing the  $AT^2$  complexities of the odd-even transposition sort with the systolic priority queue, it is found that the former is more cost effective than the latter by a factor of 2.

Extra cost incurred by bringing in fault tolerance features is minimized by exploiting the inherent properties of the embedded sorting algorithm. Properties such as nondecreasingly or nonincreasingly ordered output sequence is used to check the functional correctness of the sort-

ing array. In contrast with assuming that a faulty sorting element will transmit its inputs to the outputs unchanged or a faulty element can be located by some external circuits and then bypassed as in [25,26] and [27], a faulty sorting element in our error model can either pass or swap data incorrectly. Also, we discovered an important robust property of the odd-even transposition sorting array in which a single error can be masked automatically and multiple errors can be detected concurrently without disturbing the normal circuit operation.

In addition to checking the order of the outputs, the code-preserving property in data manipulation is employed to check whether the output data has been modified. Errors which violate the code-preserving property can be detected by using an appropriate coding technique. Depending on how critical the applications are, the requirements of fault coverage as well as the corresponding coding techniques will be different. Three example coding techniques are evaluated and the results are shown in section 2.6.

The total overhead of the proposed approach based on our analysis is much lower than previous fault tolerance techniques for other pipelined array processors [28, 29, 30], even if the checkers in the array are designed to be totally self-checking to increase the reliability. From the analysis in section 2.6, the overhead ratio is approximately (54 + c)/14N where c is a constant determined by the data error coverage requirement as well as the adopted coding technique for the array. For example, with the simple parity check code, c is equal to four and the overhead ratio is less than 10% if N is greater than 42.

#### 2.2 Array Architecture and Cell Realization

In order to have a high performance system, the two-level pipelining technique [31] which is frequently used in sorting arrays to achieve very high throughput [32,33] is employed in the design here. In addition to the use of the pipelined odd-even transposition sort as the word-level structure (section A), the systolic data flow concept [8] is used for the bit-level pipelining (section B). In this chapter, we use the term *CS element* to represent a word-level compare-swap element and the term *cell* to represent a bit-level compare-swap element. Also, without loss of generality, we will assume that the sorted output sequence is in nonincreasing order.

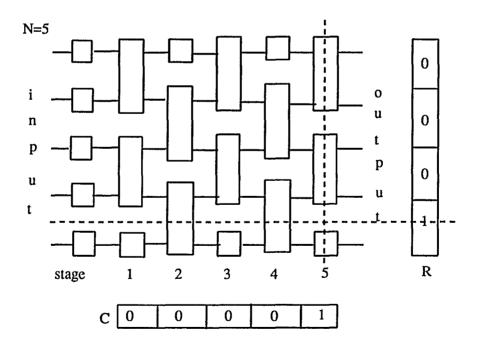

#### A. Array Architecture

The word-level pipelines can be achieved by one of the parallel sorting algorithms such as the odd-even transposition sort, the bitonic sort, the perfect shuffle sort, or the balanced sort. Based on the Aw/At ratio as discused in section 2.1, the simple and regular odd-even transposition sort is adopted. An example odd-even transposition sorter with N=5 (without loss of generality, N is assumed to be an odd number) represented by Knuth's [5] comparator-network representation is shown in Fig. 2.1. Horizontal lines represent data paths and vertical lines represent comparisons between data values. As shown in Fig. 2.1, the five inputs, 1, 2, 3, 4, and 5 are nonincreasingly ordered at the outputs as 5, 4, 3, 2, and 1. The word-level implementation of the systolic sorting array based on the odd-even transposition sort is shown in Fig. 2.2 where each vertical line in Fig. 2.1 is realized by a CS element. The parallel odd-even transposition sorting array consists of a cascade of N stages with N(N-1)/2 CS elements in each stage to sort N input data elements [5]. Each CS element in the sorting array compares two n-bit input numbers x and y and swaps these two values if x < y. Data registers (D) in Fig. 2.2 are used as

| N=5 | 1 _ | <br>2 | 2_ | 4 | 4 | 5      |

|-----|-----|-------|----|---|---|--------|

|     | 2 _ | 1     | 4  | 2 | 5 | 4      |

|     | 3   | <br>4 | 1  | 5 | 2 | 3      |

|     | 4   | 3     | 5  | 1 | 3 | —<br>2 |

|     | 5   | <br>5 | 3  | 3 | 1 | 1      |

Figure 2.1. Odd-even transposition sort: comparator-network representation.

delay buffers so that input data sets can be synchronized by the system clock and pipelined through stages of the sorting array.

Figure 2.2. Odd-even transposition sort: word-level structure.

#### B. Cell Realization

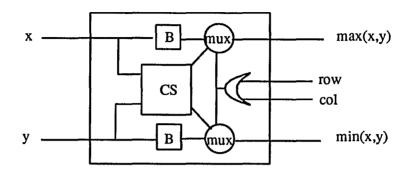

In the word-level, there are only two types of elements in the sorting array: data registers (D) and compare-swap elements (CS). For each CS element, n bit-level comparisons are required to compare two n-bit binary numbers. These n steps of comparisons can be implemented by either a serial or a parallel method. Since the goal here is to have high throughput systems, the systolic data flow concept is also applied in the bit-level pipelines. A matrix of single-bit data registers (d) is cascaded before the input stage to synchronize the data flow as shown in Fig. 2.3. (Note that this matrix of d registers is required only before the CS elements of the first stage.) These data registers are arranged as a lower right triangular matrix such that input data bits can enter the systolic sorting array in a skewed fashion. That is, for a CS element, when  $c_n$  has finished processing  $x_n$  and  $y_n$  the comparison results can pass to cell  $c_{n-1}$  together with the two inputs  $x_{n-1}$  and  $y_{n-1}$  at the same time. Therefore,  $c_n$  can process the next inputs  $a_n$  and  $b_n$  when  $c_{n-1}$  is processing  $x_{n-1}$  and  $y_{n-1}$ . The n cells of each CS element are chained together by the swap control lines r and s.

Logical operations of a cell  $c_i$  in a CS element are described in the following: (1) Signals  $s_{i+1}$  and  $r_{i+1}$  from cell  $c_{i+1}$  to cell  $c_i$  indicate whether any of the more significant bits than bit i has been swapped or not. (2) Inputs  $x_i$  and  $y_i$  are the ith bits of the two input words x and y to a CS element, respectively. (3) The signal  $r_i$  indicates whether  $(x_n, ..., x_i) = (y_n, ..., y_i)$  or not (  $r_i = 0$  or 1, respectively ) and  $s_i$  indicates whether  $(x_n, ..., x_i) < (y_n, ..., y_i)$  or not (  $s_i = 1$  or 0, respectively ). (4)  $\alpha_i$  and  $\beta_i$  are two output data bits from cell  $c_i$  with  $\alpha_i \ge \beta_i$ . Therefore, we have the bit-level cell structure and logical equations as shown in Fig. 2.4.

In the case of  $s_{i+1} = 1$ , it means  $(y_n, ..., y_{i+1}) > (x_n, ..., x_{i+1})$ . Both  $s_i$  and  $r_i$  should then be set to 1 and passed to cell  $c_{i-1}$  to indicate that x < y and cell  $c_i$  should swap the two input bits

Figure 2.3. Structure of a CS element and the matrix of data registers.

$x_i$  and  $y_i$ . Otherwise, if  $s_{i+1} = 0$  and  $r_{i+1} = 1$ ,  $(y_n, ..., y_{i+1}) < (x_n, ..., x_{i+1})$  and  $(s_i, r_i)$  should be (0, 1), i.e., no swap is needed. The case in which both  $r_{i+1}$  and  $s_{i+1}$  are zeros represents  $(y_n, ..., y_{i+1}) = (x_n, ..., x_{i+1})$  and the order of x and y will be determined by  $x_i$  and  $y_i$  in the following three cases: (1) If  $x_i = y_i$ , we have  $s_i = r_i = 0$ ,  $\alpha_i = x_i$ , and  $\beta_i = y_i$ . (2) If  $x_i < y_i$ , then  $s_i = r_i = 1$ ,  $\alpha_i = y_i$  and  $\beta_i = x_i$ . (3) Otherwise,  $s_i = 0$ ,  $r_i = 1$ ,  $\alpha_i = x_i$ , and  $\beta_i = y_i$ .

For example, let  $x = (x_n, ..., x_1)$ ,  $y = (y_n, ..., y_1)$  be two inputs of a CS element in the first stage.  $x_n$  and  $y_n$  are processed in cell  $c_n$  of the CS element first. Initially  $r_{n+1}=0$  and  $s_{n+1}=0$ . After the comparison of  $x_n$  and  $y_n$  in cell  $c_n$ , the swap control signals  $s_n$  and  $r_n$  from  $c_n$  will be passed to  $c_{n-1}$ . At the next clock,  $x_{n-1}$  and  $y_{n-1}$  together with  $s_n$  and  $r_n$  are processed in  $c_{n-1}$ , another input data set  $a_n$  and  $b_n$  is processed at  $c_n$  at the same time.

The swap control signals  $s_1$ ,  $r_1$  from cell  $c_1$  indicate whether the two inputs, x and y, have been swapped ( $s_1 = 1$ ,  $r_1 = 1$ ) or not ( $s_1 = 0$ ). We call  $s_1$  the swap-indicator since it alone can tell us if there is any swap operation performed in the corresponding stage.

#### 2.3. Properties of the Sorting Array

In order to evaluate the fault tolerance techniques, the error model which describes the effect of physical faults on the sorting element will be defined first in subsection A. The error model defined here is quite general that it can cover many faults whose nature are not apparent. Properties of the sorting array which will be exploited to introduce fault tolerance capabilities are then derived in subsection B.

#### A. Error Model

The error model is defined at the *CS* element level. A *CS* element which contains physical faults can generate errors such as swapping its inputs incorrectly, modifying the data values, or both, and can be classified as a *functional error*, a *data error*, or a *hybrid error*, respectively.

Figure 2.4. Structure of a compare-swap cell and its logical functions.

For example, stuck-at faults on the two swap control lines can cause functional errors and stuck-at faults on the communication links can cause data errors. Effect of faults on links between stages i and i+1 is lumped into stage i+1 such that errors in communication links are also representable in this word-level error model. Faults in communication links are less common [34] but more severe since, in a sorting array, a faulty communication link will cause the entire output data useless unless a reconfiguration process followed by a recovery process is applied.

Example errors are shown in Fig. 2.5 where x and y represent four-bit numbers. The example in Fig. 2.5(a) shows that the element with faulty control lines performs an incorrect swap and thus represents a functional error. An example data error is shown in Fig. 2.5(b) which indicates that the value y has been modified. A hybrid error is shown in Fig. 2.5(c). A CS element with a hybrid error will generate both incorrect order and data values at the outputs and is regarded as having multiple errors.

#### B. Properties

The first property is that the systolic sorting array based on the odd-even transposition sort with N stages and (N-1)/2 elements in each stage is a valid sorting array and a random input sequence will be correctly ordered at the outputs [35]. The second property is that the sorting array is a code-preserving sorter. This is due to the fact that the sorting array consists of CS elements and data registers only, no logical or arithmetic operation which can modify data values is performed during normal circuit operations. Therefore, the order of input sequence may be modified at the outputs but the coded input values should be preserved.

These two properties inherently exist in all sorting arrays and any sorter can be examined functionally according to these two properties. In addition to these two common properties, we

Figure 2.5. Example errors.

derive a special property for functional error checking which can be applied to all pipelined sorting algorithms and a robust property for the odd-even transposition sort only, in which any single functional error can be recovered automatically. Based on these two special properties, the sorting array can be designed with high reliability and low overhead.

It should be noted that as was discussed in subsection A, it is possible for a CS element to swap its inputs incorrectly such that the entire output sequence from a sorting array is not nonincreasingly ordered. From the comparator-network representation of the odd-even transposition sort (Fig. 2.1), we can see that two neighbor stages in the odd-even transposition sorting array completely compare all pairs of adjacent inputs in two clock cycles. Therefore, if two additional neighbor stages which include an odd-numbered stage and an even-numbered stage are added after the last stage of any sorting array, they can be used as a checker to check whether the outputs from the sorting array are ordered or not. If the output sequence is correctly ordered, no swap operation will be executed in any CS element of these two additional stages, otherwise, some of these CS elements will perform swap operations and it represents that the output sequence from the sorting array is not correctly ordered. We call these two

stages the *Nonincreasing-Order-Checker (NOC)*, and the detailed proof will be presented in Theorem 2.1.

Let  $V_1$  represent the input vector of N values to the sorting array (i.e., the input of the first stage) and  $V_h$  represent the input vector of the hth stage.  $V_h[i]$  represent the value located at the ith input line of stage h.

**THEOREM 2.1:** The nonincreasing-order-checker (*NOC*) can determine whether the output sequence from the sorting array is correctly ordered or not.

**PROOF:** The outputs of the sorting array at the Nth stage will be nonincreasingly ordered such that

$$V_{N+1}[1] \ge V_{N+1}[2] \ge V_{N+1}[3] \ge \cdots \ge V_{N+1}[N]$$

if there is no faulty CS element in the array. The CS elements in stages N+1 and N+2 of the NOC will then compare  $V_{N+1}[i]$  to  $V_{N+1}[i+1]$ , i=1 to N-1, and should not perform any swap operation. If the output from the NOC which is the ORing of the swap-indicators in these two stages is set to 1, it means that at least one of the CS elements of the NOC has made a swap operation and therefore, the output sequence from stage N is not correctly ordered.

The second property is the robust property of the odd-even transposition sort. This robust property is very important in on-line real-time applications. For on-line applications, the probability of a single error is much higher than multiple errors. If a single error can be recovered automatically without interrupting the entire system, the system availability will be increased significantly. Before we prove this property, two variables ex(i,h) and bp(i,h) are introduced first in Definition 2.1 to represent the number of exchanges and bypasses executed, respectively, if we compare  $V_h[i]$  with  $V_h[j]$ , for all j > i.

**DEFINITION 2.1:** Let  $ex(i,h) = \sum_{j=1}^{N-i} c(V_h[i]:V_h[i+j])$  where  $c(V_h[i]:V_h[i+j])=1$  if  $V_h[i] < V_h[i+j]$ , and  $c(V_h[i]:V_h[i+j])=0$ , otherwise. Similarly, let  $bp(i,h) = \sum_{j=1}^{N-i} \overline{c}(V_h[i]:V_h[i+j])$  where  $\overline{c}(V_h[i]:V_h[i+j])=1$  if  $V_h[i] \ge V_h[i+j]$  and  $\overline{c}(V_h[i]:V_h[i+j])=0$ , otherwise.

**LEMMA 2.1:** If  $\sum_{i=1}^{N-1} ex(i,h)=0$ , then the input sequence to stage h is in nonincreasing order after being processed by stages 1, 2, ..., h-1.

PROOF: Since  $ex(i,h) \ge 0$ ,  $\sum_{i=1}^{N-1} ex(i,h) = 0$  means that ex(i,h) = 0 for all i = 1 to N-1. Therefore,  $V_h[1] \ge V_h[i]$  (for  $1 < i \le N$ ) since ex(1,h) = 0, and  $V_h[2] \ge V_h[i]$  (for  $2 < i \le N$ ) since ex(2,h) = 0, and so on . . .,  $V_h[N-1] \ge V_h[N]$  since ex(N-1,h) = 0. That is,  $V_h[1] \ge V_h[2] \ge ..., \ge V_h[N]$ .

**LEMMA 2.2:**

$$ex(i,h)+bp(i,h)=N-i$$

and  $\sum_{i=1}^{N-1} ex(i,h)+\sum_{i=1}^{N-1} bp(i,h)=\binom{N}{2}=\frac{N(N-1)}{2}$

PROOF: This lemma can be proved by assuming that a *bubble sort* is applied to the input vector of stage h. Thus, the values of ex(i,h) and bp(i,h) can be viewed as the number of exchanges and bypasses, respectively, required to move the value at line i to its final position. Hence, ex(i,h)+bp(i,h)=N-i and the total number of operations required by the bubble sort to sort the corresponding input vector is equal to  $\sum_{i=1}^{N-1} N-i=\sum_{i=1}^{N-1} ex(i,h)+\sum_{i=1}^{N-1} bp(i,h)=\begin{bmatrix} N\\2 \end{bmatrix}=\frac{N(N-1)}{2}.$

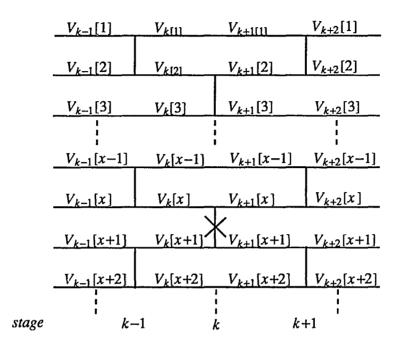

In the following analysis, we will assume that a functional error is generated by the CS element in stage k ( $k \le N$ ) which compares two inputs on lines x and x+1 (see Fig. 2.6).

**LEMMA 2.3:** For  $i\neq x$ , if  $V_k[i] < V_k[i+1]$  then ex(i,k+1) = ex(i,k) - 1 else ex(i,k) = ex(i,k+1). For i=x, if  $V_k[x] \ge V_k[x+1]$  then ex(x,k+1) = ex(x,k) + 1 else ex(x,k) = ex(x,k+1).

**PROOF:** For

$$i \neq x$$

,  $ex(i,k) = \sum_{j=1}^{N-i} c(V_k[i]:V_k[i+j])$  and  $ex(i,k+1) = \sum_{j=1}^{N-i} c(V_{k+1}[i]:V_{k+1}[i+j])$ .

From these two functions we can see that the difference between the results of ex(i,k) and ex(i,k+1) will depend on the values of  $V_k[i]$ ,  $V_k[i+1]$  and the operation of the CS element between the two lines i and i+1. Other CS elements in stage k will not affect the relationship between ex(i,k) and ex(i,k+1). If  $V_k[i] < V_k[i+1]$  and there is a CS element between lines i and i+1 then this CS element will perform an exchange operation on the two input values at the outputs. So we have  $V_{k+1}[i] (=V_k[i+1]) > V_{k+1}[i+1] (=V_k[i])$ , i.e., ex(i,k+1) = ex(i,k) - 1. Otherwise, ex(i,k) = ex(i,k+1), for  $k \le N$ .

For i=x, as the analysis in the above, the difference between ex(x,k) and ex(x,k+1) depends on the values of  $V_k[x]$ ,  $V_k[x+1]$  and the operation of the CS element between the two lines x and x+1. According to the outputs of the faulty element, this functional error can be classified as either incorrect swapping or incorrect bypassing and the corresponding relationship between ex(x,k) and ex(x,k+1) will be ex(x,k)+1=ex(x,k+1) for making an incorrect swapping or ex(x,k)=ex(x,k+1) for making an incorrect bypassing, respectively.

From the analysis of Lemma 2.3, we know that the number of exchanges required to move the value at line i of stage k to its final position is not affected by other CS elements that do not compare the two values  $V_k[i]$  and  $V_k[i+1]$ . That is the faulty CS element in stage k will not increase the number of exchanges required to move the value at line i to its final position unless i=x.

Figure 2.6. A comparator-network representation of a faulty element at stage k.

**THEOREM 2.2:** The systolic sorting array for N inputs based on the odd-even transposition sort with N+2 stages can recover from a single functional error in the first N stages automatically.

**PROOF:** Depending on the number of exchanges performed by the fault-free CS elements in stage k and the results derived in Lemma 2.3, we have the following two cases:

(1)  $\sum_{i=1}^{N-1} ex(i,k)+1=\sum_{i=1}^{N-1} ex(i,k+1)$ , that is, all the *CS* elements in stage *k* perform bypass operations except the faulty one which generates an incorrect swap. According to the configuration of the odd-even transposition sort (as shown in Fig. 2.6), we have  $V_{k+1}[1] \ge V_{k+1}[2] \ge \cdots \ge V_{k+1}[x]$  and  $V_{k+1}[x+1] \ge V_{k+1}[x+2] \ge \cdots \ge V_{k+1}[N]$ . Therefore, *CS* elements in stages k+1 and k+2 will not perform any swap operation except the one that compares  $V_{k+2}[x]$  and  $V_{k+2}[x+1]$  and it corrects the result generated by the faulty element at stage k.

Therefore,  $\sum_{i=1}^{N-1} ex(i,h) = 0$  for h > k+2 since  $V_{k+3}[1] \ge V_{k+3}[2] \ge \cdots \ge V_{k+3}[x]$ ,

$V_{k+3}[x+1] \ge V_{k+3}[x+2] \ge \cdots \ge V_{k+3}[N]$ , and  $V_{k+3}[x] \ge V_{k+3}[x+1]$ . Thus, input sequence to stage k+3 has been sorted and it will not change the order any further more in the sorting array from stages k+3 through N+2.

(2)  $\sum_{i=1}^{N-1} ex(i,k) \ge \sum_{i=1}^{N-1} ex(i,k+1)$ , that is, at least one *CS* element in stage *k* executes a swap operation in addition to the faulty one. Let  $ex_b(i,h)$  and  $ex_f(i,h)$  be equivalent to ex(i,h) and  $bp_b(i,h)$  and  $bp_f(i,h)$  be equivalent to bp(i,h) except that the subscript "b" means that the faulty stage *k* is assumed bypassed and "f" means that the faulty stage is assumed not bypassed. In the following analysis, we will complete the proof by first showing that the number of exchanges required for the faulty stage *k* is bypassed will be equal to 0 at the input of stage N+3 (i.e.,  $ex_b(i,N+3)=0$ ) and then showing that  $ex_b(i,h) \ge ex_f(i,h)$  for h>k so that we also have  $ex_f(i,N+3)=0$ .

If stage k is bypassed, the function of stage k-1 will be duplicated by stage k+1 so that stage k+1 can be viewed as bypassed. Thus, the normal execution of stage k is performed by stage k+2 and the normal execution of stage k+1 is performed by stage k+3, ..., and the normal execution of N is performed by stage N+2. So the output sequence from stage N+2 is sorted. From Lemma 2.1, we have  $\sum_{i=1}^{N-1} ex_b(i,N+3) = 0$ . By comparing  $\sum_{i=1}^{N-1} ex_b(i,h)$  with  $\sum_{i=1}^{N-1} ex_f(i,h)$  for  $k \le h \le N+3$ , we can show that  $\sum_{i=1}^{N-1} ex_b(i,h) \ge \sum_{i=1}^{N-1} ex_f(i,h)$ . The reason is described in the following: Due to the result from Lemma 2.2, we have  $\sum_{i=1}^{N-1} ex_i(i,h) + \sum_{i=1}^{N-1} bp(i,h) = {N \choose 2} = \frac{N(N-1)}{2}$ . Since the input vector  $V_k$  for assuming faulty stage k is either bypassed or not is the same. So that  $\sum_{i=1}^{N-1} bp_f(i,k) = \sum_{i=1}^{N-1} bp_b(i,k)$ . Because the input vector  $V_k$  are processed by more functionally

normal *CS* elements before arriving stage h (h>k) in the case of faulty stage k is not bypassed than in the case of stage k is bypassed, therefore, we have  $\sum_{i=1}^{N-1} bp_f(i,h) \ge \sum_{i=1}^{N-1} bp_b(i,h)$  and  $\sum_{i=1}^{N-1} ex_b(i,h) \ge \sum_{i=1}^{N-1} ex_b(i,h) \ge \sum_{i=1}^{N-1} ex_b(i,h) \ge \sum_{i=1}^{N-1} ex_b(i,h)$  and  $\sum_{i=1}^{N-1} ex_b(i,h) \ge \sum_{i=1}^{N-1} ex_b(i,h) \ge \sum_{i=1}^{N-1} ex_b(i,h) = 0$ , we have  $\sum_{i=1}^{N-1} ex_f(i,h) \ge \sum_{i=1}^{N-1} ex_f(i,h) = 0$ . Again from Lemma 2.1, we know that the outputs of stage N+2 have been sorted and therefore, the single functional error is recovered by the two extra stages.

### 2.4. Fault Tolerance

Fault tolerance techniques such as recomputing in different stages or elements [36,28,37,38], and recomputing with shifted operands [30] can detect errors in pipelined array processors, but the requirement of 100% time overhead is not tolerable in real-time applications. Therefore, we adopt the algorithm-based approach [39,40,41] to design a fault tolerant systolic sorting array with the capabilities of concurrent error detection and correction and minimize the overhead by using the properties we derived in the last section.

In subsection A, by checking the two general invariant properties, the sorting array has the capability of concurrent error detection. By exploiting the special property we derived in Theorem 2.2, the sorting array can correct a single functional error during the normal operation. It is difficult to correct data errors in a sorting array during the normal operation. Even if the faulty bits can be detected and corrected by some coding techniques [42,43,44] such as the Hamming code and the Berger code, [45] the output sequence is no longer correctly ordered. Therefore, with the assumption that the hardware used for off-line diagnosis and yield enhancement such as the multiplexers and the bypass registers in each *CS* element are fault-free, we will

present a fast on-line fault diagnosis procedure in subsection B to locate the faulty sorting elements. This assumption is appropriate because those additional circuits are usually included for the purpose of off-line testing and reconfiguration [31] in the manufacturing phase and they are fault free before operation and not activated during the normal on-line operation.

For mission-critical applications, the restart time should also be minimized and therefore, an efficient on-line reconfiguration procedure is presented in subsection C. The presented sorting array can also be degraded gracefully. As will be discussed in subsection C, it can be degraded to sort less input data and tolerate more faulty elements if it runs out of redundancy.

#### A. Concurrent Error Detection and Correction

As proved in Theorem 2.1, whether the output sequence is in nonincreasing order or not can be detected by the *NOC*. Error correction for a single functional error is done automatically as shown in Theorem 2.2. Therefore, the two stages added to a sorting array can be either a checker or a single error corrector. These two stages are sufficient for a single error. But for multiple errors, two more stages are required to detect other errors after the first error has been corrected by the first two added stages.

The problem of who will check the checkers is very important in mission critical applications. The two additional stages used to recover a single error in the array will not be able to recover errors in themselves. The errors in the *NOC* itself will generate a useless result if the *NOC* does not have a self-checking capability to check its own outputs. Therefore, from Theorems 2.1 and 2.2, the sorting array for N inputs can be implemented with N+4 stages for error detection and correction. The first N stages are for normal sorting functions. Stages N+3 and N+4 are used as the NOC and will be designed to be *totally self -checking (TSC)* [46]. (The details on implementing a TSC checker will be discussed in section 2.5). Stages N+1 and

N+2 which are used to correct a single functional error do not need to be TSC circuits since their outputs are checked by stages N+3 and N+4 (NOC). However, in the following theorem, we will show that stage N+4 can be omitted from the sorting array if stage N+2 is implemented by TSC circuits.

**THEOREM 2.3:** The systolic sorting array with a total of three additional stages, stages N+1, N+2 and N+3, where stages N+2 and N+3 are implemented by TSC circuits can tolerate one incorrect swap operation and check whether the output sequence is nonincreasingly ordered or not.

**PROOF:** From the properties derived in Theorems 2.1 and 2.2, a systolic sorting array with a total of four additional stages has the capability to tolerate one incorrect swap operation and to check whether the output sequence is ordered or not. In the following analysis, we will prove that if stages N+2 and N+3 are implemented with TSC circuits, the stages N+1 and N+2 can be used to correct a single functional error and stage N+3 itself can be used to detect multiple functional errors in the sorting array.

According to the properties of TSC circuits [46], the checkers implemented as TSC circuit are code disjoint, fault secure, and self-testing. If stage N+2, which compares  $V_{N+2}[1]$  and  $V_{N+2}[2]$ ,  $V_{N+2}[3]$  and  $V_{N+2}[4]$ , ...,  $V_{N+2}[N-2]$  and  $V_{N+2}[N-1]$ , is implemented as TSC circuits, we should have  $V_{N+3}[1] \ge V_{N+3}[2]$ , ...,  $V_{N+3}[N-2] \ge V_{N+3}[N-1]$  at the output of stage N+2 due to the fault secure property, otherwise, errors in this stage will be detected by the stage itself. Therefore, if the output sequence is nonincreasingly ordered at the output of stage N+2, then stage N+3 which takes this sequence as input and compares  $V_{N+3}[2]$  and  $V_{N+3}[3]$ , ...,  $V_{N+3}[N-1]$  and  $V_{N+3}[N]$ , should not do any swap operation, otherwise, the output sequence is not ordered. This shows that stage N+4 can be omitted.

In addition to checking the correctness of the output order, we can check whether the input data values are preserved during the normal operation or not by using appropriate coding techniques. The choice of a data error detection method is very flexible depending on the properties of the sorting array, the type of errors to be detected, and the fault coverage requirement. Arithmetic codes such as residue code[47] have good fault coverage for all kinds of errors, but they require large devices. Coding techniques for error detection in communication lines such as Berger code and modified Berger code [48] require less area overhead but they are efficient in detecting unidirectional errors only. Fault coverages and overhead analysis for different options in coding techniques will be discussed in section 2.6.

#### B. On-Line Fault Diagnosis

We have proved (in Theorem 2.2) that whether the fault-free CS elements in the faulty stage k are bypassed or not, two extra stages are required any way to mask the effect of a faulty CS element in the faulty stage k ( $k \le N$ ), i.e., the fault-free CS element in the faulty stage are useless. Therefore, instead of locating individual faulty elements, the on-line fault diagnosis procedure only needs to identify the location of the entire faulty stage and this makes our reconfiguration procedure simpler.

The diagnosis procedure is described in Fig. 2.7. The input set I which generates the data error is reapplied repeatly to diagnose the faulty stage. A reservation table which shows an example diagnosis for a sorting array with N=5 and three extra stages is in Table 2.1 where DED represents a data error detector. A marked entry at the (n, m)th position of the table indicates that the stage K=n will be activated m time units later after the initiation of the fault-diagnosis procedure. Empty spaces in the table represent idle stages that perform only bypass operation.

```

Procedure On Line Fault Diagnosis;

begin

roll back input data I;

/* I is the inputs which generate the data error */

k=1:

/* k is used to control which stages should be bypassed */

for t: = 1 to N+3 do begin

/* t represents the clock sequence */

if t is odd then k = k+1;

input I and bypass stages k to N+3;

end:

for t:= N+4 to 2(N+3) do begin

if data error detector is set at t

then stage t - (N+3) is faulty;

end;

end.

/* all stages process data normally except the stages

specified to be bypassed */

```

Figure 2.7. On-line fault diagnosis procedure.

At t=1, the input set I is applied and processed at stage 1 (we call it  $I_{11}$  to represent that it is reapplied into the sorting array at t=1 and has been processed by stage 1) and will pass through all the other stages without being processed. The bypassing capability of a CS element and a stage will be discussed in the next section. At t=2, the same input set I is applied again to stage 1 (we call it  $I_{21}$ ) and  $I_{11}$  will not be processed until t=9. That is,  $I_{11}$  bypasses stages 2 to 8 and is then checked by DED. At t=3, the same input set I is applied again to stage 1 (we call it  $I_{21}$ ), and at the same time  $I_{21}$  enters stage 2 (we call it  $I_{22}$ ). After this,  $I_{22}$  will not be processed until it is checked by DED at t=10. Thus, for t=1, 2, ..., N+3, these reapplied inputs are processed at stage 1, stages 1 through 2, ..., stages 1 through N+3, respectively, such that the data set I which generates incorrect data at the outputs due to a faulty CS element in stage m will set the data error indicator at time t=N+3+m during the on-line fault diagnosis.

This faulty stage m will then be bypassed by the on-line reconfiguration process (as will be discussed in subsection C) to exclude the faulty element from normal operation before the sorting array can get back into normal operation.

Therefore, instead of a time consuming off-line diagnosis and reconfiguration, we can restore the array back into operation with a time delay of 2(N+3) clocks (we assume that this sorting array is used as a special chip attached to a large system and this system has buffers large enough to store N+3 input data sets). The reconfigured sorting array with one faulty stage bypassed can no longer correct a single functional error but can still detect multiple functional errors. This procedure can be generalized to any sorting array with more than three extra stages by simply increasing the values of the loop control variables with appropriate constants.

Table 2.1. Reservation table.

|             |                                 | K                 |                   |                                   |                                    |                                    |                 |      |                                    |  |

|-------------|---------------------------------|-------------------|-------------------|-----------------------------------|------------------------------------|------------------------------------|-----------------|------|------------------------------------|--|

| t_          | 1                               | 2                 | 3                 | 4                                 | 5                                  | 6                                  | 7               | 8    | DED                                |  |

| 1 2 3       | $I_{11} I_{21}$                 |                   |                   |                                   |                                    |                                    |                 |      |                                    |  |

| 3<br>4<br>5 | $I_{31}$ $I_{41}$               | $I_{22}$ $I_{32}$ |                   |                                   |                                    |                                    |                 |      |                                    |  |

| 5           | I <sub>51</sub>                 | I <sub>42</sub>   | I <sub>33</sub>   |                                   |                                    |                                    |                 |      |                                    |  |

| 6           | I <sub>61</sub> I <sub>71</sub> | $I_{52} I_{62}$   | $I_{43} = I_{53}$ | I <sub>44</sub>                   |                                    |                                    |                 |      |                                    |  |

| 8           | I 81                            | $I_{72}$          | I 63              | $I_{54}$                          | ,                                  |                                    |                 |      | ,                                  |  |

| 9<br>10     |                                 | I <sub>82</sub>   | $I_{73}$ $I_{83}$ | I <sub>64</sub><br>I <sub>7</sub> | I <sub>55</sub><br>I <sub>65</sub> |                                    |                 |      | $I_{11}$ $I_{22}$                  |  |

| 11          |                                 |                   | <b></b>           | I <sub>84</sub>                   | $I_{75}$                           | I <sub>66</sub>                    |                 |      | $I_{33}$                           |  |

| 12<br>13    |                                 |                   |                   |                                   | I <sub>85</sub>                    | I <sub>76</sub><br>I <sub>86</sub> | 177             |      | I <sub>44</sub><br>I <sub>55</sub> |  |

| 14          |                                 |                   |                   |                                   |                                    | - 80                               | I <sub>87</sub> |      | I <sub>66</sub>                    |  |

| 15<br>16    |                                 |                   |                   |                                   |                                    |                                    |                 | I 88 | I <sub>77</sub><br>I <sub>88</sub> |  |

Although this on-line fault diagnosis procedure is designed to locate the faulty stage which generates data errors, by adding some extra hardware this procedure can be adapted to locate the faulty element which generates either a functional error or a data error. Since each data word contains the check bits, if we can access these check bits we can identify the faulty sorting element in stage m when a data error is detected at t=(N+3)+m. To locate the faulty elements generating a functional error, both swap-indicators of stage N+2 and stage N+3 should be checked. These two stages are activated and bypassed alternately so that inputs at t=1, 3, ..., N are checked by stage N+2 and inputs at t=2, 4, ..., N+1 are checked by stage N+3 respectively. If some of the sorting elements in stage m are faulty, the corresponding sorting elements in stage N+2 (m is odd) or N+3 (m is even) will set the swap-indicators at time t=(N+3)+m.

### C. On-Line Reconfiguration and Performance Degradation

In order to achieve fast on-line reconfiguration, bypass registers (B) and multiplexers (mux) (see Fig. 2.8) which are usually added to a processing element for manufacturing reconfiguration [31] are utilized in our on-line reconfiguration. The multiplexer can be enabled by two control lines, row bypass (r) or column bypass (c). In the normal operation, (r, c) is reset as (0, 0) and outputs from the CS elements are selected. If a CS element is faulty, it is bypassed by setting either r or c to 1. In order to reduce the cost of bypass control circuitry, only the word-level control scheme is considered as shown in Fig. 2.9 where a CS element is bypassed when either the corresponding bit in the row bypass control register or the column bypass control register is set to 1. All bypass control lines of cells in the same CS element are set or reset together. Each bit of the row bypass control register controls all CS elements in the same row and each bit of the column bypass control register controls all CS elements in the same column (stage). The entire sorting array can also be degraded to sort N-1, N-2 or less

Figure 2.8. Compare-swap element with bypass registers and switches.

inputs as shown in Fig. 2.9. Two dotted lines in row 4 and stage 5 of Fig. 2.9 means that CS elements are bypassed in the corresponding row and column and the sorting array can then be used to sort N-1 inputs.

Figure 2.9. System degradation scheme.

# 2.5. Design of Totally Self-Checking Checkers

We have designed a data error detector and an *NOC* to detect data errors and functional errors, respectively, in the last section. It is always desirable to design checkers which can detect errors in the checker itself as well as in its inputs. This leads us to design checkers which are totally self-checking (*TSC*). The concept of a totally self-checking checker has been introduced in [49] as a circuit which is fault secure, self-testing, and code disjoint [46].

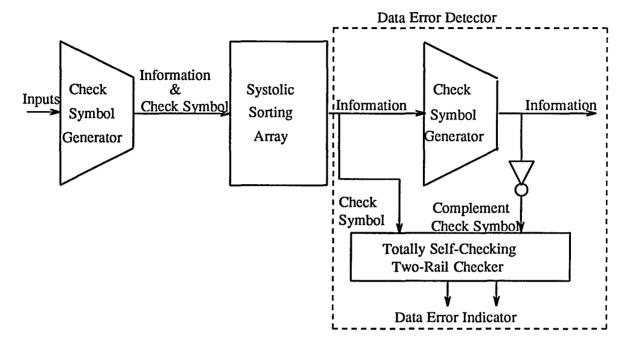

### A. Design of a Totally Self-Checking Data Error Detector

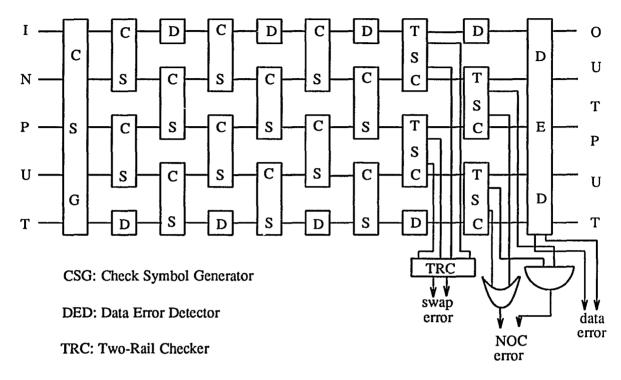

A general structure of the totally self-checking data error detector for the systolic sorting array is shown in Fig. 2.10. Check bits from the *check symbol generator* (CSG) are generated based on the coding technique used. They are attached to the corresponding data (information) and propagated through the array but are not processed by the systolic sorting array before arriving the *two-rail checker* (TRC) (TRC is a two-level AND-OR circuit as in [46] and will be described latter). At outputs, these input check symbols are compared with the outputs from the *complement check symbol generator* ( $\overline{CSG}$  is a combination of CSG which generates check bits for the received data and an inverter at the output of each check bit) through a tree of two-rail checkers. As discussed in the previous section that any input data should not be modified by the systolic sorting array, so the check symbols generated by the  $\overline{CSG}$  should be complementary to the check symbols generated by the CSG if both the checker and the sorting array are fault-free.

In the case that only one check bit is generated for each codeword (for example, by using the single parity code to detect data error), since N inputs will be processed in parallel, N 1-out-of-2 code outputs ((01) or (10) for code word outputs and (00) or (11) for noncode word

Figure 2.10. Totally self-checking data error detector.

outputs) will be generated in parallel during normal operations. Therefore, a tree of two-rail checkers which maps N input pairs into one output pair can be used to combine these information together and generate a single output (10) or (01) in the normal operation and (00) or (11) as an error message. In order to have a high fault coverage, usually more than one check bit of each data will be generated by the CSG and  $\overline{CSG}$  (for example, by using either the Berger code, the modified berger code, or the low-cost code) and therefore, an intermediate-level two-rail checker is required for each code word to map the outputs of check symbols and complement check symbols into a single output pair. Sometimes, the combination of inverters of the  $\overline{CSG}$  and the intermediate-level two-rail checkers are called an *equality checker* [46] because it can check whether the input check symbols are the same as the output check symbols or not.

Design of a *TSC* checker for single bit parity code is quite simple. Let  $x = (x_n, ..., x_1)$  be the input data and the code word output from the odd parity generator is  $(x_n, ..., x_1, x_0)$ . Divide the set of variables into two groups,  $(x_n, x_{n-2}, ..., x_1)$  and  $(x_{n-1}, x_{n-3}, ..., x_0)$ , and connect variables of each group to the inputs of the parity checker. During the normal operation, the number of 0's in the former group is odd and that in the latter is even, or vice versa. Therefore, for a fault-free output data the outputs of the two parity checker will be either (10) or (01) but never (00) and (11). Verification of the self-checking properties for this checker was given in [49].

Designs of a totally self-checking checker for the modified Berger code and a self-checking checker for the Berger code were presented in [48] and [50] respectively. To avoid the problem of two legal representations of zero during the calculation of residues, either special definitions are required for the modulo  $2^m$ -1 adder in the check symbol generator [51] (where  $2^m$ -1 is the check base of the residue code) or a code translator is added between the equality checkers and the two-rail checkers [52] to design an efficient TSC checker for the low-cost code.

It has been proved that the two-rail checker is a totally self-checking checker [46]. The combination of the CSG and the  $\overline{CSG}$  can be a totally self-checking checker for different coding techniques such as for the simple parity code, [49] the modified Berger code, [48] the Berger code, [50] and the low-cost code [51,52]. Since the output pair from the CSG and  $\overline{CSG}$  can generate all 0, 1 sequences needed to test the two-rail checker tree, the combination of these two circuits preserves properties of TSC [46].

# B. Design of a Totally Self-Checking Order Checker

To design a *TSC CS* element, the concept of duplication with comparison is used to generate m-variable ( $m = \frac{N-1}{2}$ ) two-rail code (or 1-out-of code). Every Boolean function f(x) has a corresponding dual function  $f_d(x)$  such that  $f_d(\overline{x}) = \overline{f}(x)$ . If we apply x to the function f and  $\overline{x}$  to the function  $f_d$ , the resulting output should be complementary to each other and can be used as inputs to a *TSC* two-rail checker. The dual of a Boolean function is found by replacing AND operations with OR operations, OR operations with OR operations, OR operations with OR operations, OR operations are simple combinational circuits. Hence it is possible to duplicate all the cells in the last two stages with complementary circuitry. This can be further simplified since outputs OR and OR are checked by the data error detector. Therefore, only the output information OR and OR which indicate whether the cell OR performs swap or not should be duplicated in order to design the OR elements. These OR elements which are implemented according to the above method of designing OR circuit will generate paired OR swap—indicators in the form of the 1-out-of-2 code. That is, if a OR element has a functional error, its output pair OR will be either OR or

The stage N+2 which is used to correct a functional error should be designed as TSC checkers as proved in Theorem 2.3. All output pairs of  $(s_1, \overline{s}_1)$  from word-level TSC CS elements in this stage will be either (01) if there is no swap operation or (10) if there is any swap operation performed during normal operations and (00) or (11) if there is an error in a CS element. Since these 0,1 sequences can completely test the two-rail checker (TRC) tree which are used to map N output pairs to form a single output pair, the combination of TSC CS elements with TSC two-rail checker constitutes a TSC checker. The output pair from the two-rail checker

indicates whether there are functional errors (output pair is (11) or (00)) in this stage or not (output pair is (01) or (10)).

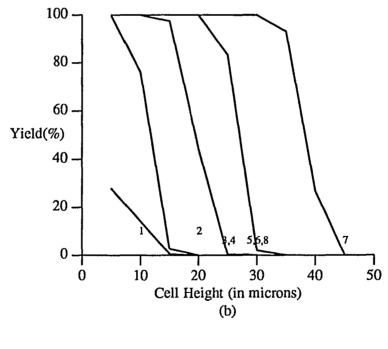

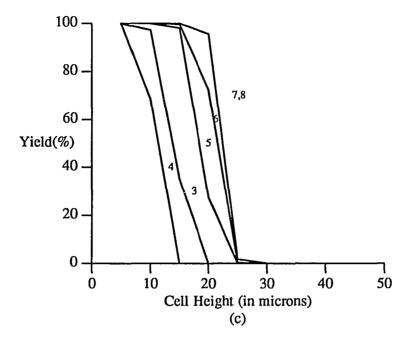

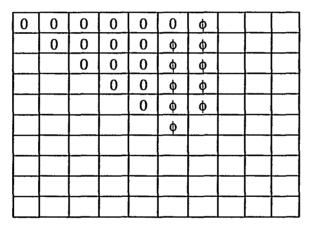

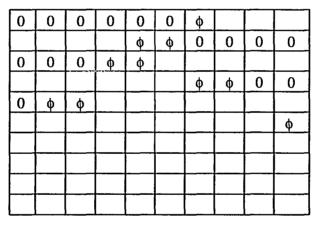

In addition to stage N+2, CS elements in stage N+3 are also designed as TSC circuits to generate m-variable two-rail code such that if there is no functional error in this stage, then the paired output  $(s_1, \overline{s}_1)$  of each CS element is either (01) or (10). In addition, if the input sequence to this stage has been ordered correctly, then the swap-indicators of all CS elements in this stage should be all 0's and their complement signals are then all 1's, i.e., the paired output  $(s_1, \overline{s}_1)$  for all CS elements are (01).