# Integrated Switching DC-DC Converters with Hybrid Control Schemes

By

Feng Luo

Copyright © Feng Luo 2009

A Dissertation Submitted to the Faculty of the

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

In Partial Fulfillment of the Requirements

For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College

THE UNIVERSITY OF ARIZONA

# THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE

As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Feng Luo entitled **Integrated Switching DC-DC Converters with Hybrid Control Schemes** and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy

|                                                                                                                          | Date: <u>05/26/2009</u>                    |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Dr. Dongsheng Ma                                                                                                         |                                            |

|                                                                                                                          | Date: <u>05/26/2009</u>                    |

| Dr. Roman Lysecky                                                                                                        |                                            |

|                                                                                                                          | Date: <u>05/26/2009</u>                    |

| Dr. Susan Lysecky                                                                                                        |                                            |

|                                                                                                                          | Date: <u>05/26/2009</u>                    |

| Mr. Bob Atwell                                                                                                           |                                            |

| Final approval and acceptance of this dissertation is cont. the final copies of the dissertation to the Graduate College |                                            |

| I hereby certify that I have read this dissertation prepared<br>be accepted as fulfilling the dissertation requirement.  | I under my direction and recommend that it |

|                                                                                                                          | Date: <u>05/26/2009</u>                    |

| Dissertation Director: Dr. Dongsheng Ma                                                                                  |                                            |

### STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library. Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the head of the major department or the Dean of the Graduate College when in his or her judgment the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the copyright holder.

| SIGNED: |          |  |

|---------|----------|--|

|         |          |  |

|         | Feng Luo |  |

### **ACKNOWLEDGEMENTS**

This dissertation could not have been completed without Dr. Dongsheng Ma who not only served as my supervisor but also encouraged and challenged me throughout my entire graduate academic life. He patiently guided me through the dissertation process, never accepting less than my best efforts. Because of his constant encouragement and continuous support throughout my doctor program I could have remained highly motivated to carry on my research. In his inspiration, my academic career was very successful. Even more, his advice and guidance brought me stand into this advance in the field of analog integrated circuits. I am very proud for being one of the students of such a talented and personable professor.

I would like to thank some of the other excellent faculty members at the University of Arizona who have shaped my experience. I would like to thank Dr. Roman Lysecky and Dr. Susan Lysecky for many interesting discussions, for severing on my oral defense committee, and for their feedback on this dissertation. I am grateful to Dr. Meiling (Janet) Wang for her teaching and her support for being her teaching assistant. I am especially thankful to Dr. Hal S. Tharp for the incredible teaching and for his encouragement and advice.

I would also like to thank the industry collaborators, Mr. Bob Atwell, and Paul Prazak from Texas Instruments, Dr. Siamak Abedinpour from Freescale Semiconductor, and Dr. Fabrice Paillet from Intel Corporation for valuable discussion and technical support.

I would also like to express my enormous thanks to my colleagues Ling Su, Inshad Chowdhary, Hio Leong Chao, Zongqi Hu, Minkyu Song, and Mohankumar Nachimuthu Somasundaram from Integrated System Design Lab for their unwavering support, great assistance, and challenge through our variable collaborated works. They were always very active and helpful to others with their very talented suggestions.

In addition, I would like to thank my fellow students Chen Zheng, Rajdeep Bondade, Yikai Wang and Yi Zhang for their help and guidance.

Throughout my studying life, my parents and my wife Shu Zhang have always support me with love, care and encouragement unconditionally. I dedicate this dissertation to them. I am so fortunate to be with them. Without their boundless love, I would never have had the strength and courage to pursue my dreams.

### **AUTOBIOGRAPHY**

**Feng Luo** received the B.S. and M.S. degrees in electrical science and engineering from Nanjing University, Nanjing, China, in 2001 and 2004, respectively, and his Ph.D degree in electrical and computer engineering at the University of Arizona in 2009.

After graduation, Luo will join the Texas Instruments, Tucson, AZ, as a design engineer. His research interests include high speed analog and mixed signal integrated circuit, integrated power management system design, and digital VLSI design.

Luo received the Graduate College Fellowship at the University of Arizona in 2005, Excellent Graduate Scholarship at Nanjing University in 2003, and Excellent Undergraduate Scholarship at Nanjing University in 1998 and 1999, respectively.

### **TABLE OF CONTENTS**

| LIST ( | OF FIGURES                                          | 10    |

|--------|-----------------------------------------------------|-------|

| LIST ( | OF TABLES                                           | 16    |

| ABSTI  | RACT                                                | 17    |

| CHAP'  | TER 1 INTRODUCTION                                  | 19    |

| 1.1    | Motivation                                          | 19    |

| 1.2    | Research Goals and Contributions                    | 20    |

| 1.3    | Dissertation Organization                           | 21    |

| CHAP'  | TER 2 DC-DC CONVERTER FOR LOW-POWER EMBEDDED SYST   | EMS24 |

| 2.1    | Introduction on DC-DC Converter                     | 24    |

|        | 2.1.1 DC-DC Converter Specifications                | 25    |

|        | 2.1.2 DC-DC Converter Circuits                      | 27    |

|        | A. Linear Regulator                                 | 27    |

|        | B. Switched-Capacitor Power Converter (Charge Pump) | 30    |

|        | C. Switch Mode DC-DC Converter                      | 32    |

|        | 2.1.3 Switch Mode DC-DC Converter Topology          | 33    |

| 2.2    | Control Methodology in Switch Mode DC-DC Converter  | 35    |

|        | 2.2.1 Voltage-Mode PWM Control                      | 35    |

|        | 2.2.2 Current-Mode PWM Control                      | 36    |

|        | 2.2.3 Hysteresis Control (Band-Band Control)        | 39    |

|        | 2.2.4 Analog Control and Digital Control            | 40    |

| 2 3    | Power Reduction and Efficiency Enhancement          | 42    |

|      | 2.3.1 Dynamic Voltage Scaling (DVS)                          | 42      |

|------|--------------------------------------------------------------|---------|

|      | 2.3.2 Multiple Output Power Converters                       | 44      |

|      | 2.3.3 Single-Inductor Multiple-Output (SIMO) DC-DC Converter | 46      |

| СНАР | TER 3 AN INTEGRATED SWITCHING DC-DC CONVERTER WIT            | H DUAL- |

| MODE | PULSE-TRAIN/PWM CONTROL                                      | 54      |

| 3.1  | Review of Prior Arts                                         | 55      |

| 3.2  | The Proposed Dual-Mode PT/PWM Control                        | 59      |

|      | 3.2.1 Control Scheme                                         | 59      |

|      | 3.2.2 System Stability                                       | 60      |

|      | A. System Stability in PT Mode                               | 60      |

|      | B. System Stability in PWM Mode                              | 62      |

|      | 3.2.3 Output Ripple Voltage in PT Mode                       | 65      |

|      | A. Output Ripple Voltage in PT Mode                          | 65      |

|      | B. Output Ripple Voltage in PWM Mode                         | 66      |

| 3.3  | System Design & Circuit Implementations                      | 68      |

|      | 3.3.1 Closed-Loop System Architecture                        | 68      |

|      | 3.3.2 The PT Controller                                      | 69      |

|      | 3.3.3 Transistor-Scaling Current Sensor                      | 70      |

|      | 3.3.4 Clock & Ramp Generator                                 | 72      |

|      | 3.3.5 Dead-Time Controlled Buffer                            | 73      |

| 3.4  | Experimental Verifications                                   | 74      |

|      | 3.4.1 Measurement Results in the PT Mode                     | 76      |

|      | 3.4.2 Measurement Results in the PWM Mode                    | 79      |

| 3 5  | Conclusions                                                  | 81      |

| CHAP  | TER 4 DESIGN OF DIGITAL TRI-MODE ADAPTIVE-OUTPUT B       | UCK-BOOST  |

|-------|----------------------------------------------------------|------------|

| POWE  | R CONVERTER FOR POWER-EFFICIENT INTEGRATED SYSTE         | MS82       |

| 4.1   | Design Challenges and Motivations                        | 83         |

| 4.2   | Digital Tri-Mode Control Scheme                          | 85         |

|       | 4.2.1 Power-Scalable Digital Sliding Mode Control        | 85         |

|       | 4.2.2 Tri-Band Hysteresis Current-Mode Start-Up Control  | 91         |

|       | 4.2.3 Adaptive Digital Hysteresis Control                | 96         |

| 4.3   | System Architecture & Circuit Implementations            | 97         |

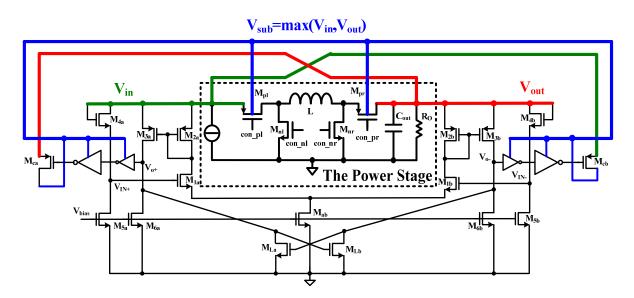

|       | 4.3.1 Closed-Loop System Architecture                    | 97         |

|       | 4.3.2 Automatic Substrate Switching Circuit (ASSC)       | 98         |

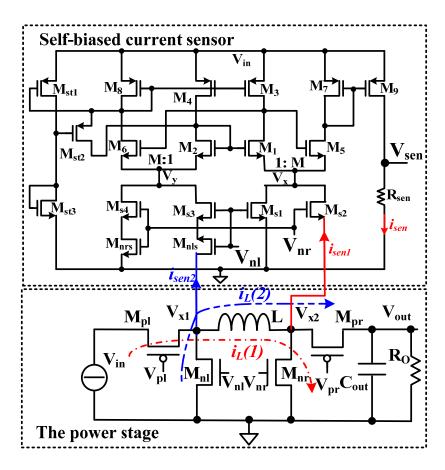

|       | 4.3.3 Self-Biased Current Sensor                         | 100        |

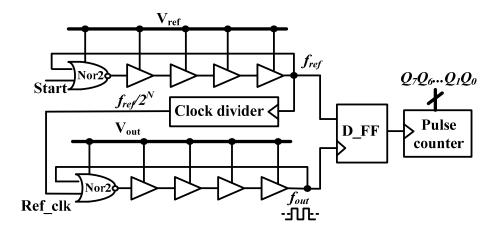

|       | 4.3.4 Ring Oscillator Based V-to-f Converter             | 103        |

|       | 4.3.5 I-to-f Converters                                  | 105        |

|       | 4.3.6 Programmable Voltage Reference Generators          | 107        |

| 4.4   | Experimental Verifications                               | 109        |

|       | 4.4.1 Steady-State Measurements                          | 109        |

|       | 4.4.2 Automatic Substrate Switching Circuit Measurements | 112        |

|       | 4.4.3 DVS/Load Transient Measurements                    | 113        |

| 4.5   | Conclusions                                              | 116        |

| CHAP  | TER 5 DIGITAL SIMO STEP-UP/DOWN POWER CONVERTE           | R FOR DVS- |

| ENABI | LED MULTICORE SYETEMS                                    | 117        |

| 5.1   | Design Motivations                                       | 118        |

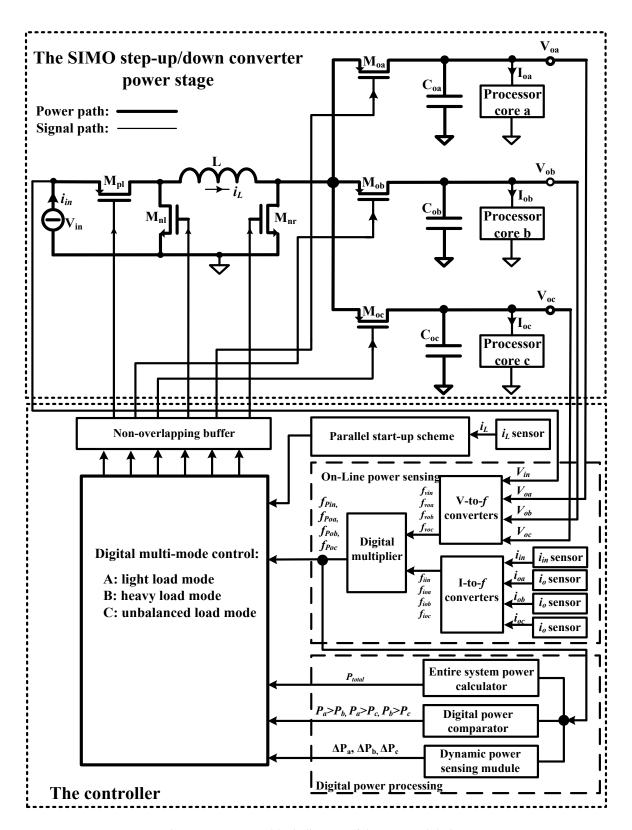

| 5.2   | System Architecture & Control Algorithms                 | 119        |

|       | 5.2.1 Closed-Loop System Architecture                    | 119        |

| 5.2.3 Software-Defined Multi-Modes Control Scheme       124         5.3 Circuit Implementations       127         5.3.1 Process and Temperature Independent Ring Oscillator Based ADC       127         5.3.2 On-Line Power Sensing and Processing       130         5.4 Performance Verifications       134         5.4.1 Steady-State Performance       134         5.4.2 Dynamic Transient Performance       137         5.5 Conclusions       140         CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1 Conclusions       141         6.2 Summary of Research Contributions       142         6.3 Future Work       143         6.3.1 Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2 Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155 |       | 5.2.2 Parallel Start-Up Control Scheme                              | 122 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------|-----|

| 5.3.1 Process and Temperature Independent Ring Oscillator Based ADC       127         5.3.2 On-Line Power Sensing and Processing       130         5.4 Performance Verifications       134         5.4.1 Steady-State Performance       134         5.4.2 Dynamic Transient Performance       137         5.5 Conclusions       140         CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1 Conclusions       141         6.2 Summary of Research Contributions       142         6.3 Future Work       143         6.3.1 Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2 Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                   |       | 5.2.3 Software-Defined Multi-Modes Control Scheme                   | 124 |

| 5.3.2 On-Line Power Sensing and Processing       130         5.4 Performance Verifications       134         5.4.1 Steady-State Performance       134         5.4.2 Dynamic Transient Performance       137         5.5 Conclusions       140         CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1 Conclusions       141         6.2 Summary of Research Contributions       142         6.3 Future Work       143         6.3.1 Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2 Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                         | 5.3   | Circuit Implementations                                             | 127 |

| 5.4       Performance Verifications       134         5.4.1       Steady-State Performance       137         5.5       Conclusions       140         CHAPTER 6       CONCLUSIONS AND FUTURE WORK       141         6.1       Conclusions       141         6.2       Summary of Research Contributions       142         6.3       Future Work       143         6.3.1       Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2       Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                                                                                      |       | 5.3.1 Process and Temperature Independent Ring Oscillator Based ADC | 127 |

| 5.4.1 Steady-State Performance       134         5.4.2 Dynamic Transient Performance       137         5.5 Conclusions       140         CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1 Conclusions       141         6.2 Summary of Research Contributions       142         6.3 Future Work       143         6.3.1 Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2 Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                                                                                                                                      |       | 5.3.2 On-Line Power Sensing and Processing                          | 130 |

| 5.4.2 Dynamic Transient Performance       137         5.5 Conclusions       140         CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1 Conclusions       141         6.2 Summary of Research Contributions       142         6.3 Future Work       143         6.3.1 Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2 Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                                                                                                                                                                                       | 5.4   | Performance Verifications                                           | 134 |

| 5.5       Conclusions       140         CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1       Conclusions       141         6.2       Summary of Research Contributions       142         6.3       Future Work       143         6.3.1       Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2       Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                                                                                                                                                                                                         |       | 5.4.1 Steady-State Performance                                      | 134 |

| CHAPTER 6 CONCLUSIONS AND FUTURE WORK       141         6.1 Conclusions       141         6.2 Summary of Research Contributions       142         6.3 Future Work       143         6.3.1 Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2 Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 5.4.2 Dynamic Transient Performance                                 | 137 |

| 6.1       Conclusions       141         6.2       Summary of Research Contributions       142         6.3       Future Work       143         6.3.1       Reconfigurable SI-MIMO Power Converter       143         A. SI-MIMO Power Stage       143         B. Bi-Directional Power Path Performance       148         6.3.2       Thermal Sensing and Thermal Shutdown Circuit       150         APPENDIX: PUBLICATION LIST       155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.5   | Conclusions                                                         | 140 |

| 6.2 Summary of Research Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CHAP  | TER 6 CONCLUSIONS AND FUTURE WORK                                   | 141 |

| 6.3 Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1   | Conclusions                                                         | 141 |

| 6.3.1 Reconfigurable SI-MIMO Power Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.2   | Summary of Research Contributions                                   | 142 |

| A. SI-MIMO Power Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.3   | Future Work                                                         | 143 |

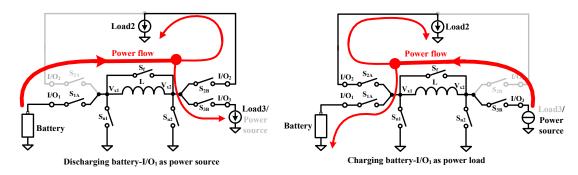

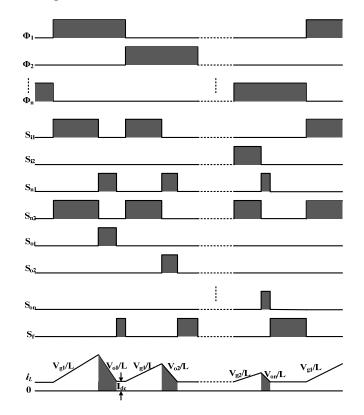

| B. Bi-Directional Power Path Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | 6.3.1 Reconfigurable SI-MIMO Power Converter                        | 143 |

| 6.3.2 Thermal Sensing and Thermal Shutdown Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | A. SI-MIMO Power Stage                                              | 143 |

| APPENDIX: PUBLICATION LIST155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | B. Bi-Directional Power Path Performance                            | 148 |

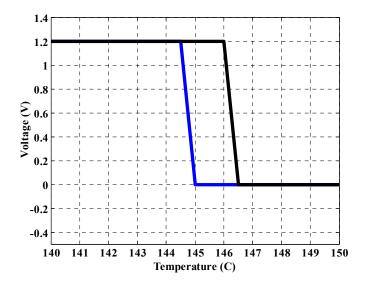

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 6.3.2 Thermal Sensing and Thermal Shutdown Circuit                  | 150 |

| REFERENCES156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | APPEN | DIX: PUBLICATION LIST                                               | 155 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | REFER | RENCES                                                              | 156 |

## **LIST OF FIGURES**

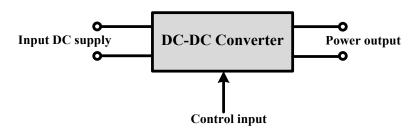

| Figure 2.1.1 System schematic of DC-DC converter.                                         | 24       |

|-------------------------------------------------------------------------------------------|----------|

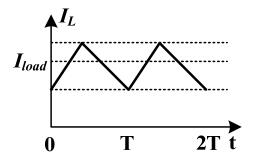

| Figure 2.1.2 Inductor current in CCM.                                                     | 26       |

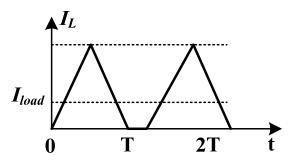

| Figure 2.1.3 Inductor current in DCM.                                                     | 27       |

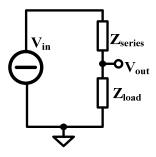

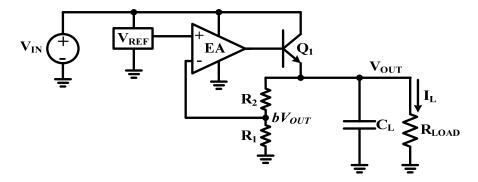

| Figure 2.1.4 Schematic of a series regulator.                                             | 28       |

| Figure 2.1.5 Schematic of a series voltage regulator.                                     | 28       |

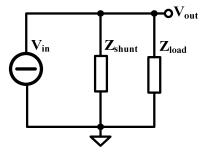

| Figure 2.1.6 Schematic of a shunt regulator.                                              | 29       |

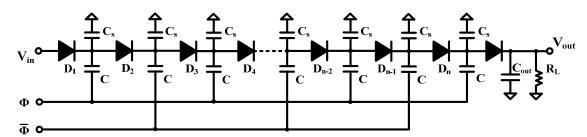

| Figure 2.1.7 Schematic of Dickson charge pump.                                            | 30       |

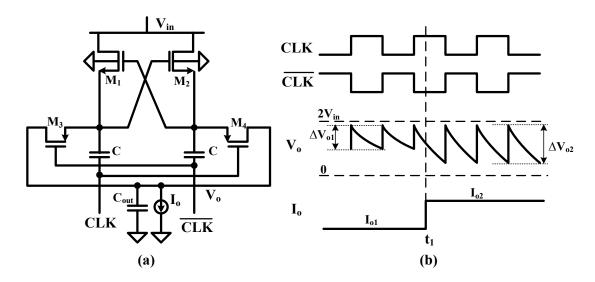

| Figure 2.1.8 (a) Schematic of a cross-coupled voltage doubler, (b) major waveforms in vol | ltage    |

| doubler                                                                                   | 31       |

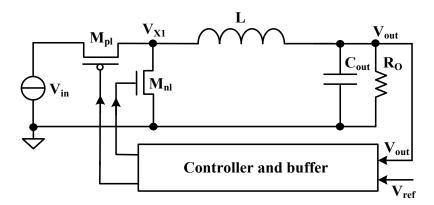

| Figure 2.1.9 Schematic of a switch mode buck converter.                                   | 32       |

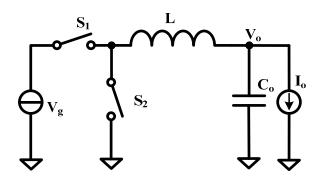

| Figure 2.1.10 Switched mode DC-DC converter topologies: buck converter.                   | 33       |

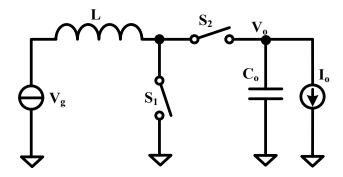

| Figure 2.1.11 Switched mode DC-DC converter topologies: boost converter.                  | 33       |

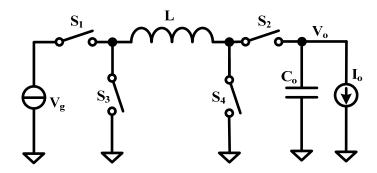

| Figure 2.1.12 Switched mode DC-DC converter topologies: buck-boost converter              | 33       |

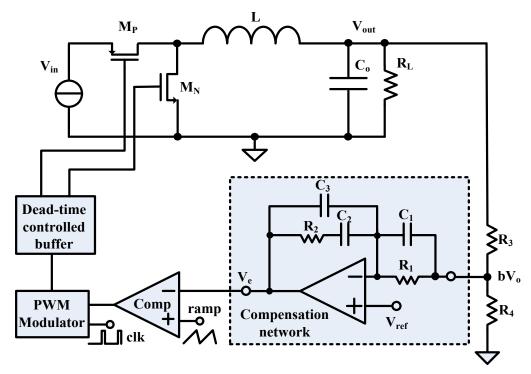

| Figure 2.2.1 Schematic of conventional voltage mode PWM controlled buck converter         | 36       |

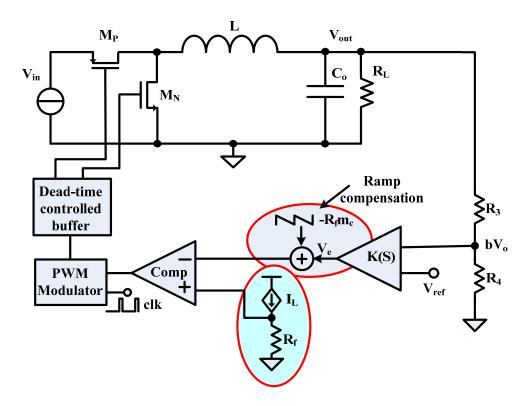

| Figure 2.2.2 Schematic of conventional current mode PWM controlled buck converter         | 37       |

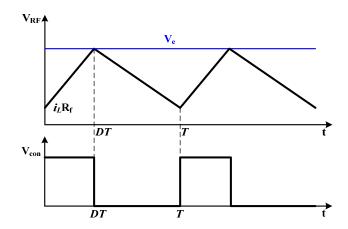

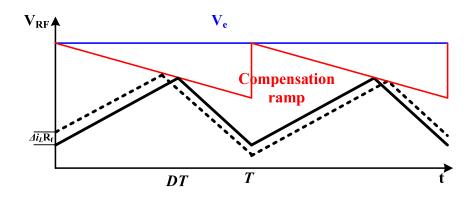

| Figure 2.2.3 Waveforms of the control signals in current mode control.                    | 38       |

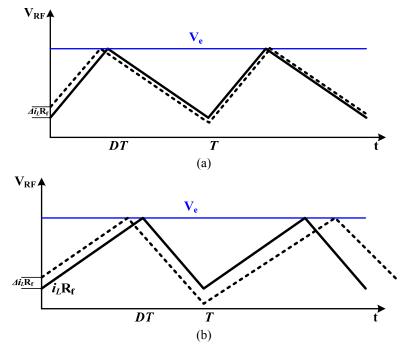

| Figure 2.2.4 Effect of small disturbances with current mode control: (a) D<0.5 (b) D>0.5. | 38       |

| Figure 2.2.5 Extra compensation ramp is added for sub-harmonic oscillation.               | 39       |

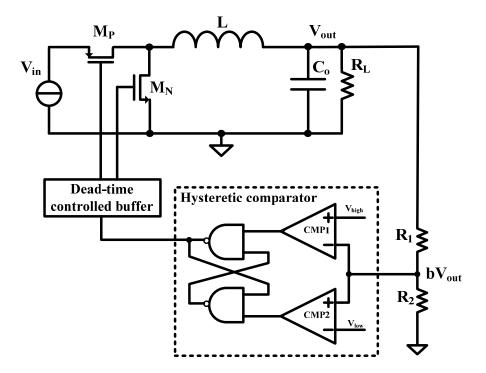

| Figure 2.2.6 Block diagram of the voltage mode hysteresis controlled buck converter       | 40       |

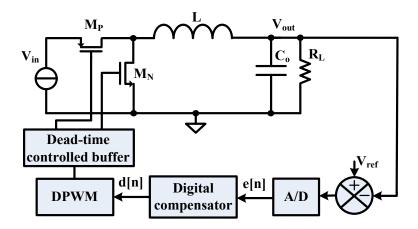

| Figure 2.2.7 Block diagram of digital voltage mode control.                               | 41       |

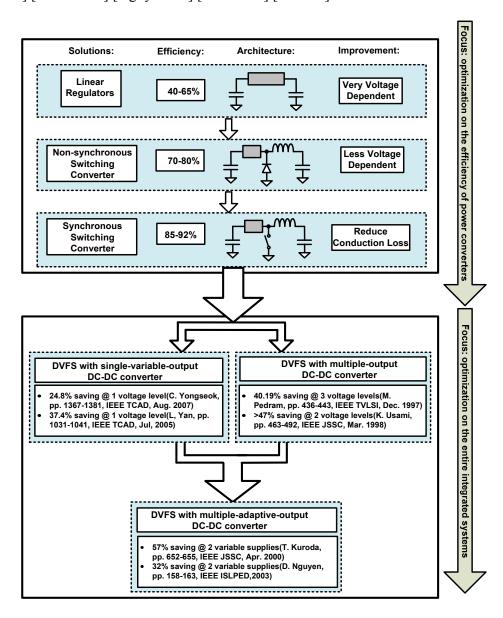

| Figure 2.3.1 Evolution of power converters and power management ICs                       | 43       |

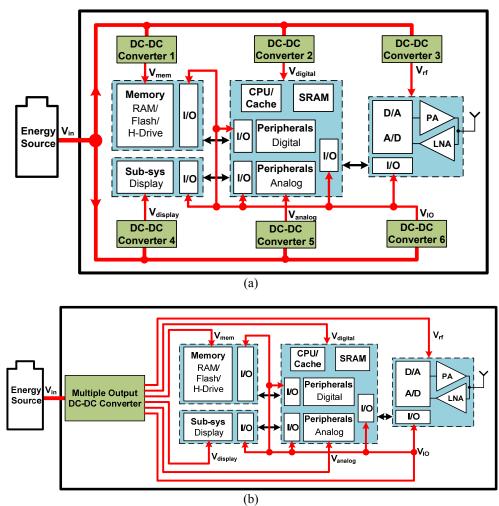

| Figure 2.3.2 A VLSI system that has six supply voltage levels: (a) needs six DC-DC con    | verters, |

| and (b) needs one six-output DC-DC converter.                                             | 45       |

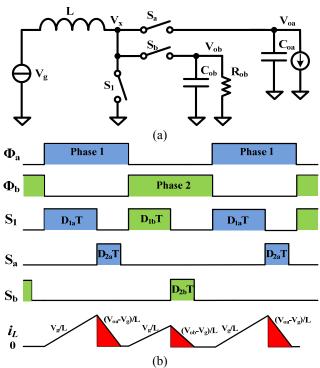

| Figure 2.3.3 SIDO boost/boost converter working in DCM using time multiplexing in [M      | [a-03a]: |

| (a) power stage, and (b) timing diagram.                                                  | 47       |

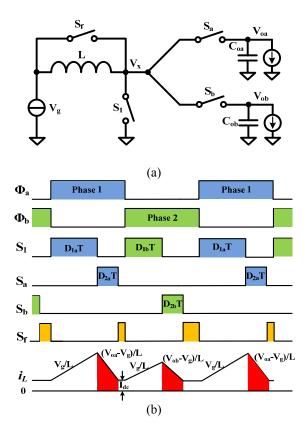

| Figure 2.3.4 SIDO boost/boost converters working in PCCM using freewheel switching in     | in [Ma-  |

| 02a]: (a) power stage, and (b) timing diagram.                                            | 48       |

| Figure 2.3.5 Cross regulation in SIMO converters.                                         | 49       |

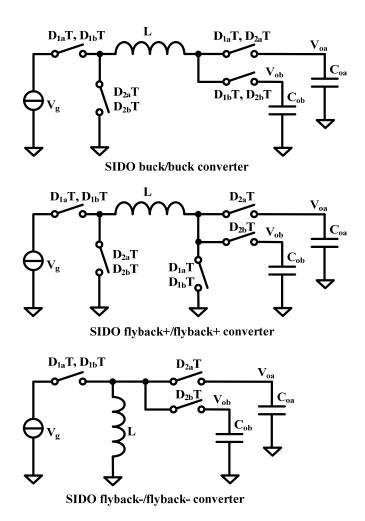

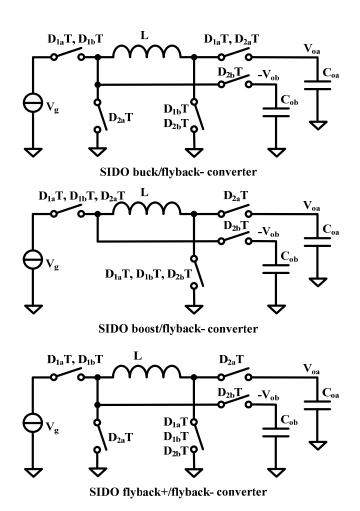

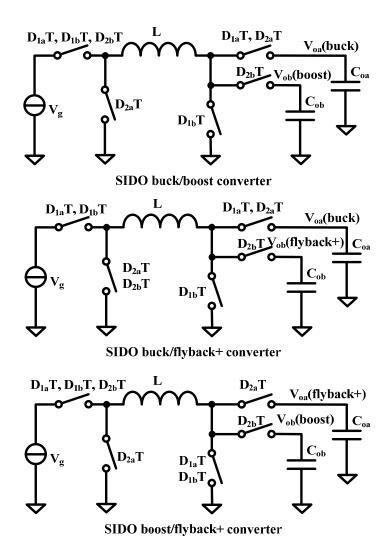

| Figure 2.3.6 Architecture extensions on SIDO switching converters: SIDO same-type co            | onverter. |

|-------------------------------------------------------------------------------------------------|-----------|

|                                                                                                 | 50        |

| Figure 2.3.7 Architecture extensions on SIDO switching converters: SIDO bipolar conve           | rter 51   |

| Figure 2.3.8 Architecture extensions on SIDO switching converters: SIDO mixed-type co           | onverter. |

|                                                                                                 | 52        |

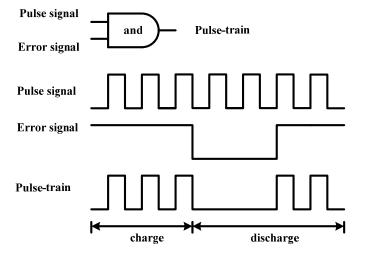

| Figure 3.1.1 Pulse-train control scheme in [Ferdowsi].                                          | 56        |

| Figure 3.1.2 The PT control scheme proposed in [Zhang-04].                                      | 56        |

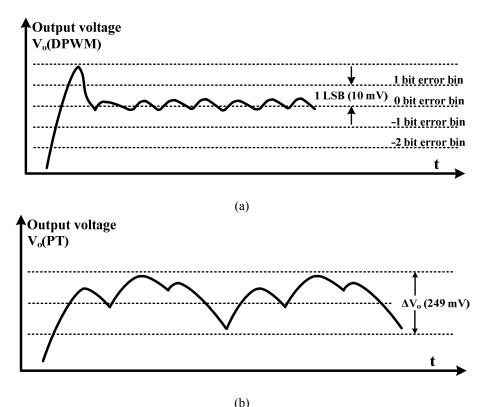

| Figure 3.1.3 Limit cycle problems at the output voltage of $V_{\text{o}}$ in (a) a DPWM s       | witching  |

| converter [Peterchev], and (b) a PT switching converter [Ferdowsi]                              | 57        |

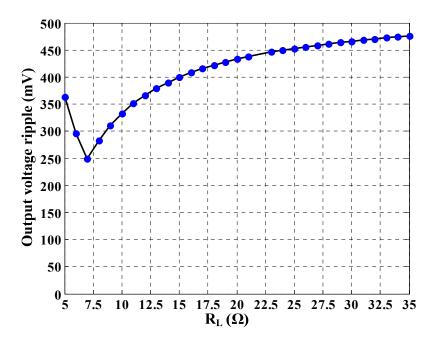

| Figure 3.1. 4 Optimal output ripple voltage versus load resistance, with multiple power a       | nd sense  |

| pulse options in [Ferdowsi]                                                                     | 58        |

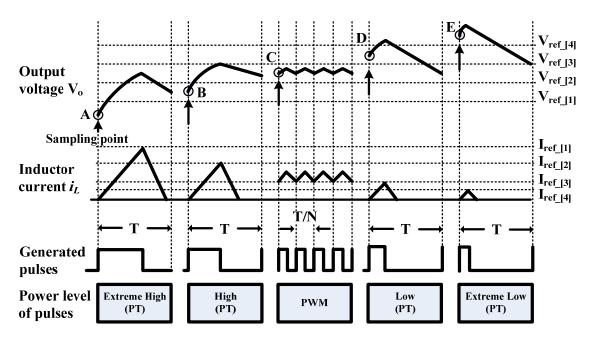

| Figure 3.2.1 The proposed dual-mode PT/PWM control scheme.                                      | 59        |

| Figure 3.2.2 Sequential flow of the PT pulse control.                                           | 62        |

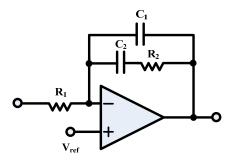

| Figure 3.2.3 Error amplifier with pole-zero compensation                                        | 64        |

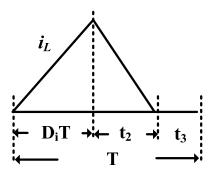

| Figure 3.2.4 One switching period in PT mode.                                                   | 65        |

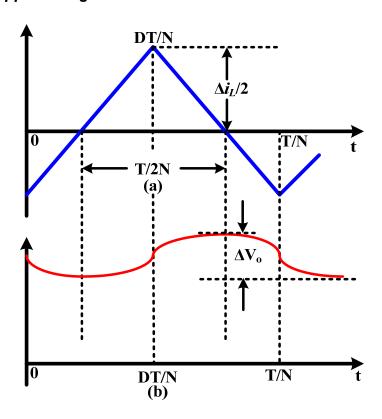

| Figure 3.2.5 (a) Output capacitor current $i_{CL}$ , and (b) output ripple voltage $\Delta V_0$ | 66        |

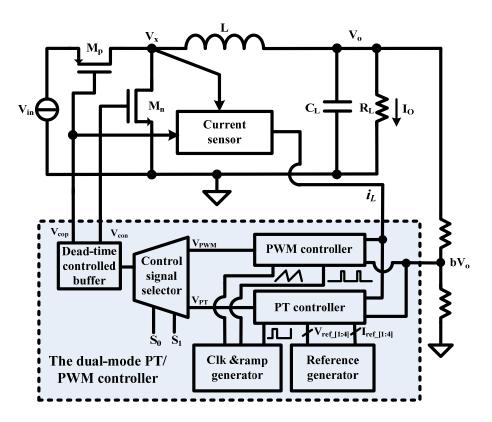

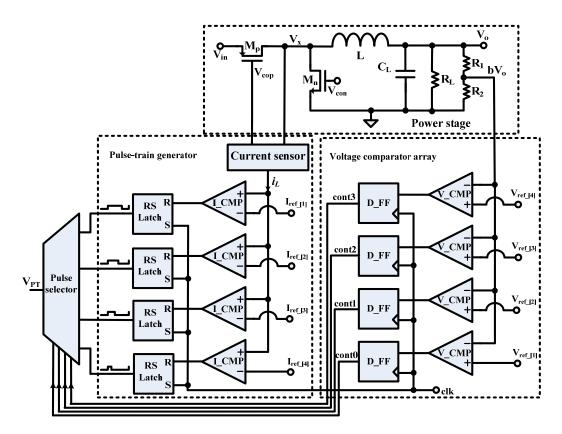

| Figure 3.3.1 Block diagram of the proposed converter.                                           | 68        |

| Figure 3.3.2 Schematic of the PT controller.                                                    | 69        |

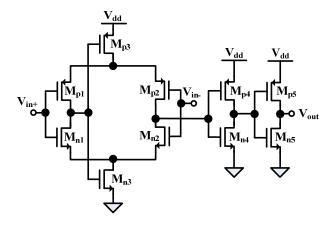

| Figure 3.3.3 Schematic of the comparator.                                                       | 70        |

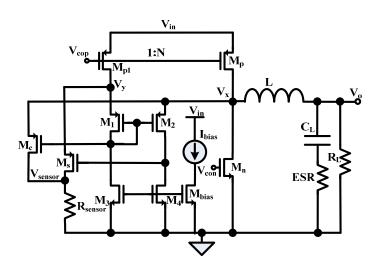

| Figure 3.3.4 Current sensor with transistor scaling.                                            | 70        |

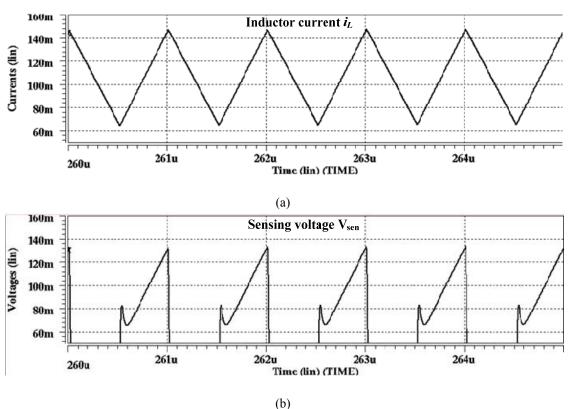

| Figure 3.3.5 (a) Simulated inductor current $i_{L_1}$ and (b) sensing voltage $V_{\text{sen}}$  | 71        |

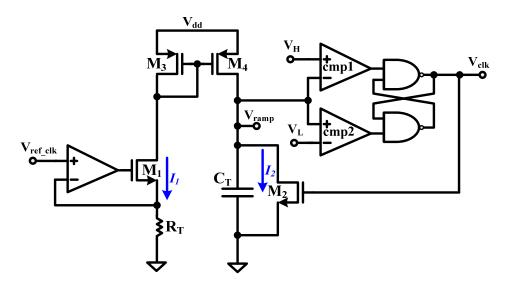

| Figure 3.3.6 Schematic of the clock and ramp generator.                                         | 72        |

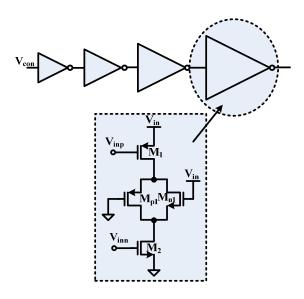

| Figure 3.3.7 Block diagram of the dead-time controlled buffer.                                  | 73        |

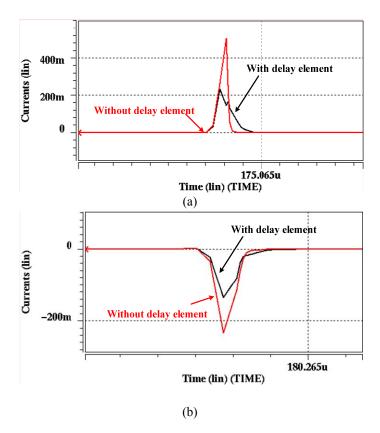

| Figure 3.3.8 Simulated current in the inverter with & without delay element: (a) current is     | n nMOS    |

| transistor, and (b) current in pMOS transistor.                                                 | 74        |

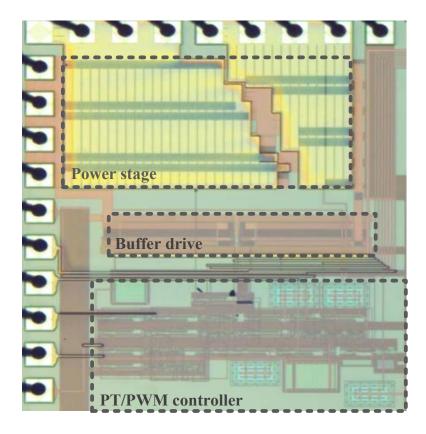

| Figure 3.4.1 Chip micrograph.                                                                   | 75        |

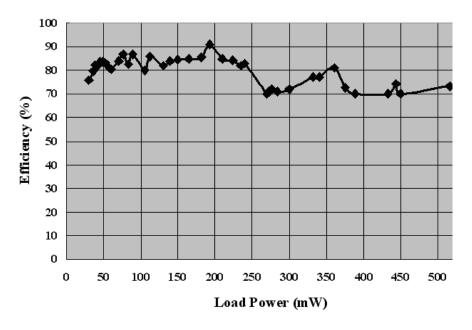

| Figure 3.4.2 Measured efficiency of the converter.                                              | 75        |

| Figure 3.4.3 Measured steady-state $V_0$ and $i_L$ at the PT mode.                              | 76        |

| Figure 3.4.4 Measured ripple voltage with reference to $i_L$ at the PT mode.                    | 77        |

| Figure 3.4.5 Measured load transient response at the PT mode: (upper) load current $i_O$ s      | witching  |

| between 50 mA and 100 mA, (lower) output V <sub>o</sub> .                                       | 77        |

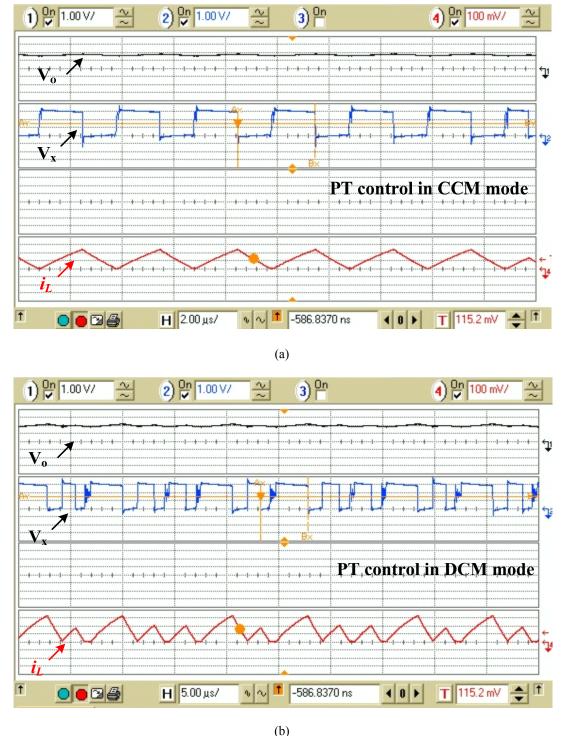

| Figure 3.4.6 Measured $V_0$ , $V_x$ , and $i_L$ at the PT control: (a) CCM mode, and (b) DCM mode                                | . 78               |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------|

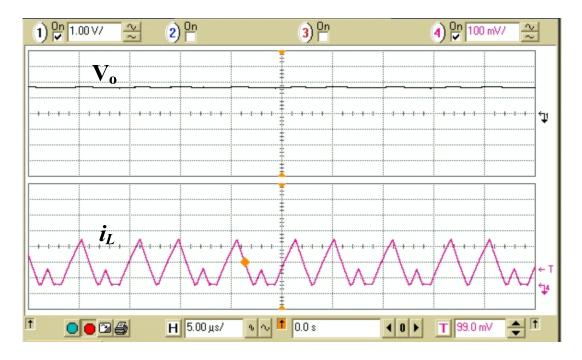

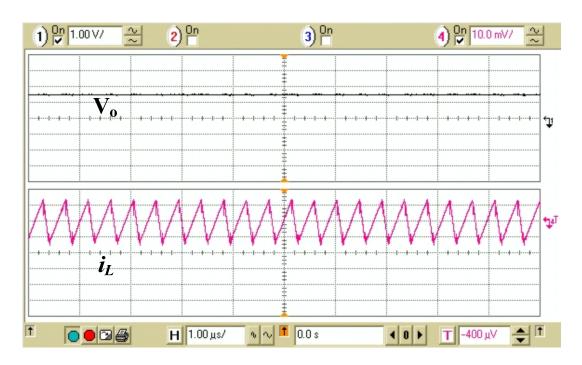

| Figure 3.4.7 Measured steady-state $V_0$ and $i_L$ at the PWM mode.                                                              | . 79               |

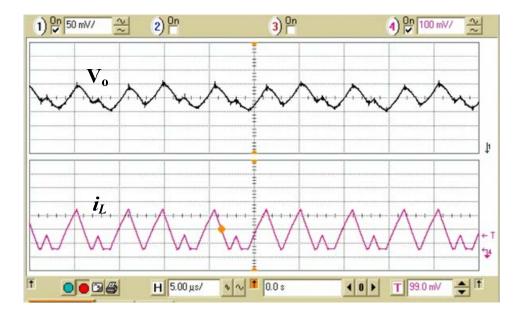

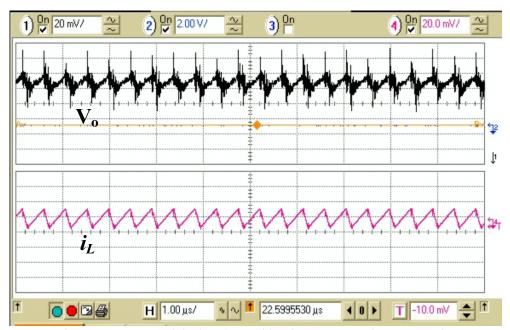

| Figure 3.4.8 Measured ripple voltage with reference to $i_L$ at the PWM mode.                                                    | . 80               |

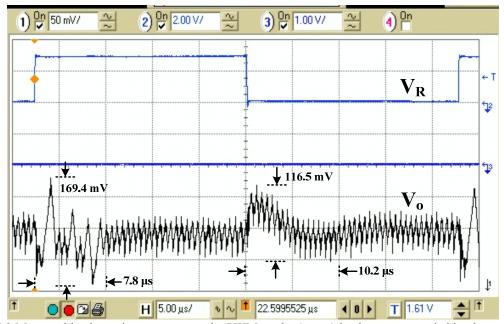

| Figure 3.4.9 Measured load transient response at the PWM mode: (upper) load current                                              | $t i_C$            |

| switching between 50 and 100 mA, (lower) output voltage V <sub>o</sub>                                                           | . 80               |

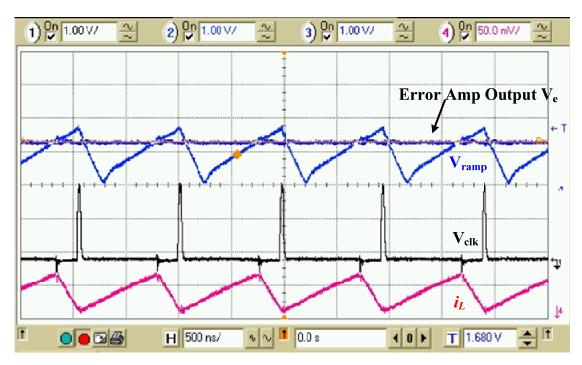

| Figure 3.4.10 Measured error amplifier output $V_e$ , ramp signal $V_{\text{ramp}}$ , clock signal $V_{\text{clk}}$ ,            | and                |

| inductor current <i>i</i> <sub>L</sub> at the PWM mode.                                                                          | . 81               |

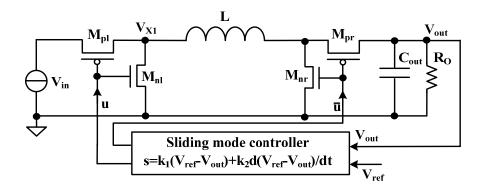

| Figure 4.2.1 Analog sliding mode controller with a buck-boost converter.                                                         | . 85               |

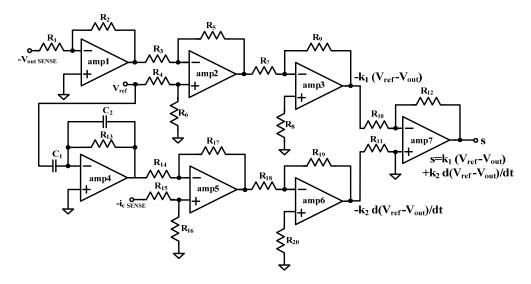

| Figure 4.2.2 One implementation of the analog sliding mode controller in [Bilalovic]                                             | . 86               |

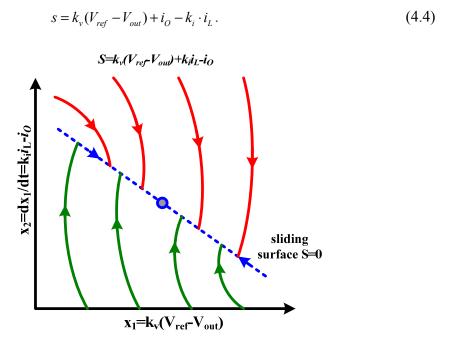

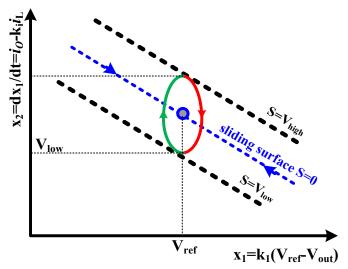

| Figure 4.2.3 Phase plane plot of the sliding rule                                                                                | . 88               |

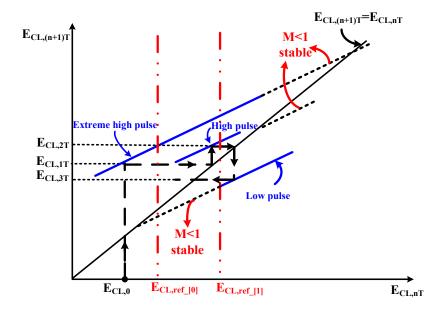

| Figure 4.2.4 The phase plane of the limit cycle.                                                                                 | . 89               |

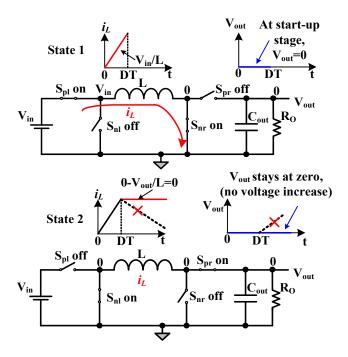

| Figure 4.2.5 Start-up issue in buck-boost converter.                                                                             | . 91               |

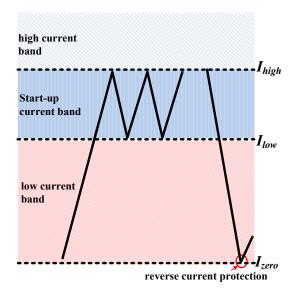

| Figure 4.2.6 Tri-band current-mode start-up scheme.                                                                              | . 92               |

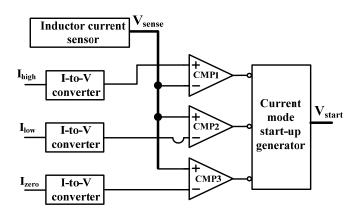

| Figure 4.2.7 Block diagram of tri-band current-mode start-up scheme.                                                             | . 93               |

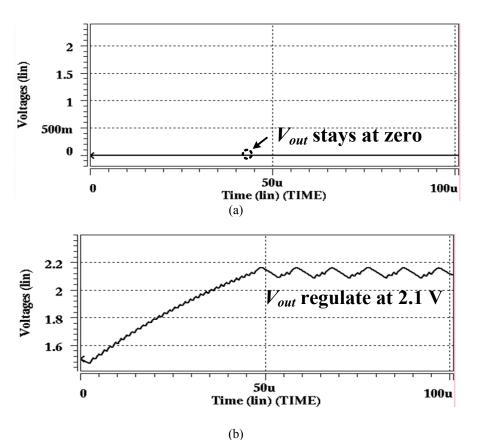

| Figure 4.2.8 Simulated output voltage $V_{out}$ , (a) without start-up control, and (b) with the propo                           | sed                |

| tri-band current-mode start-up control.                                                                                          | . 94               |

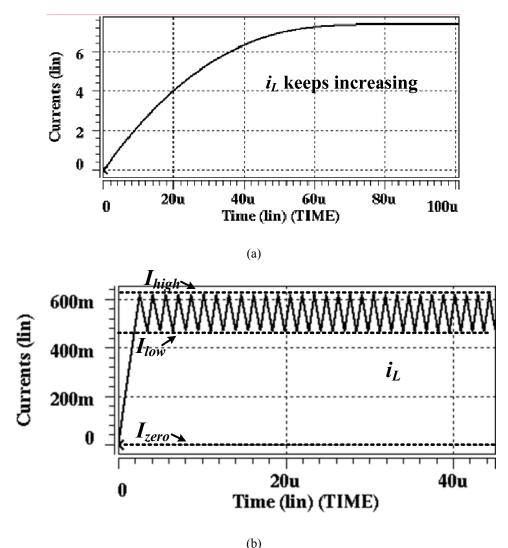

| Figure 4.2.9 Simulated inductor $i_L$ , (a) without start-up control, and (b) with the proposed                                  | tri-               |

| band current-mode start-up control.                                                                                              | . 95               |

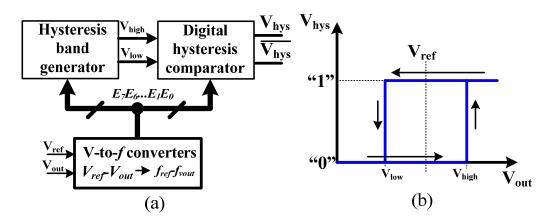

| Figure 4.2.10 (a) Block diagram, and (b) control mechanism of digital hysteresis voltage-m                                       | ode                |

| control.                                                                                                                         | . 96               |

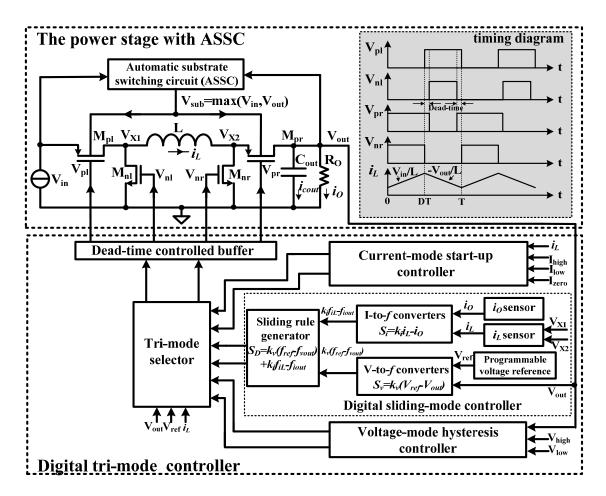

| Figure 4.3.1 Block diagram of the proposed buck-boost converter.                                                                 | . 98               |

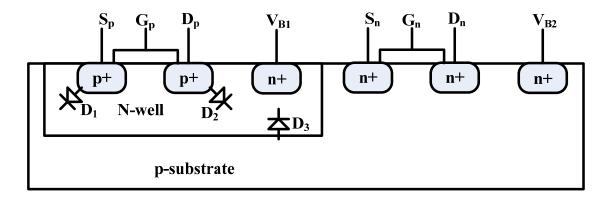

| Figure 4.3.2 Cross section of n-well CMOS process.                                                                               | . 99               |

| Figure 4.3.3 Schematic of automatic substrate switching circuit.                                                                 | . 99               |

| Figure 4.3.4 Schematic of the self-biased transistor-scaling current sensor.                                                     | 101                |

| Figure 4.3.5 Simulated self-biased current sensor waveforms: (a) inductor current, and                                           | (b)                |

| sensing voltage                                                                                                                  | 103                |

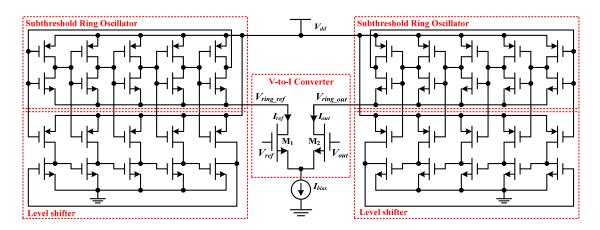

| Figure 4.3.6 Schematic of the ring oscillator based V-to- <i>f</i> converter                                                     | 103                |

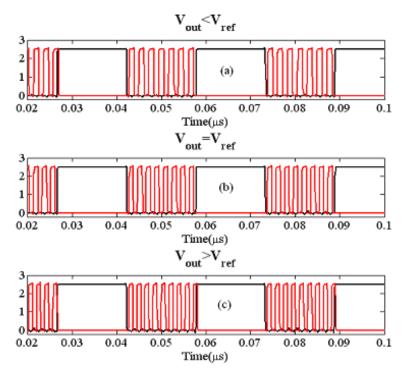

| Figure 4.3.7 Simulated V-to- $f$ converter, when (a) $V_{out} < V_{ref}$ , (b) $V_{out} = V_{ref}$ , and (c) $V_{out} > V_{out}$ | V <sub>ref</sub> . |

|                                                                                                                                  | 105                |

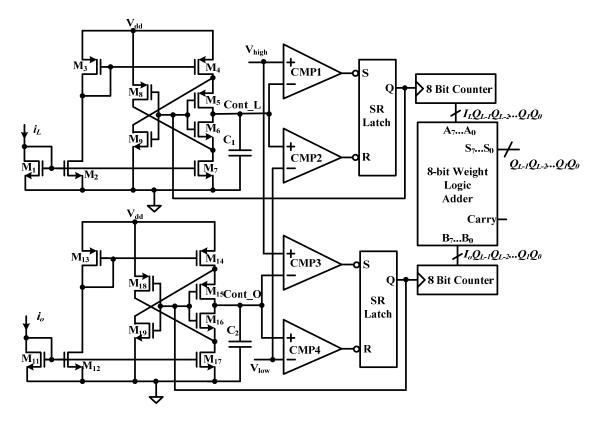

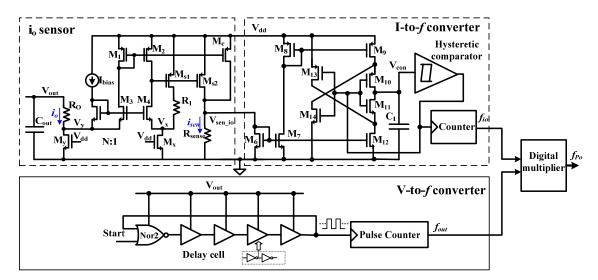

| Figure 4.3.8 Schematic of the I-to- <i>f</i> converters.                                                                         | 106                |

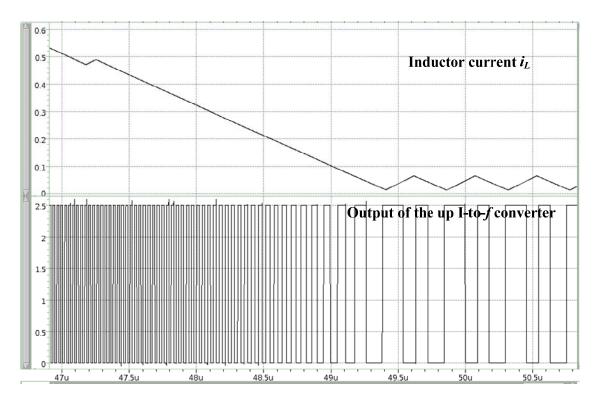

| Figure 4.3.9 Simulation result of the clock frequency linearly proportioned to it                                                | 107                |

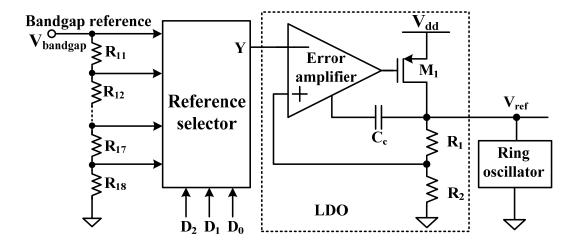

| Figure 4.3.10 Schematic of programmable voltage reference generator.                       | 108       |

|--------------------------------------------------------------------------------------------|-----------|

| Figure 4.3.11 Simulation result of programmable voltage reference generator.               | 108       |

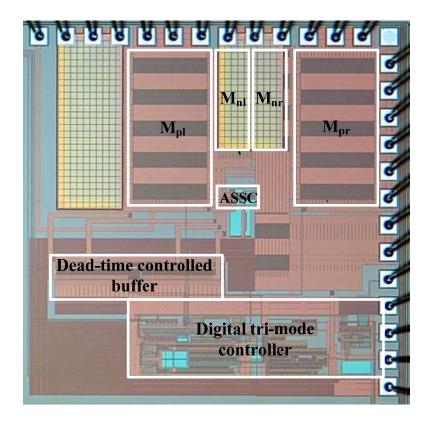

| Figure 4.4.1 Chip micrograph.                                                              | 109       |

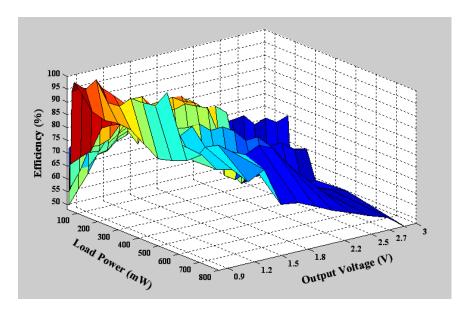

| Figure 4.4.2 Measured efficiency versus output voltage and load power.                     | 109       |

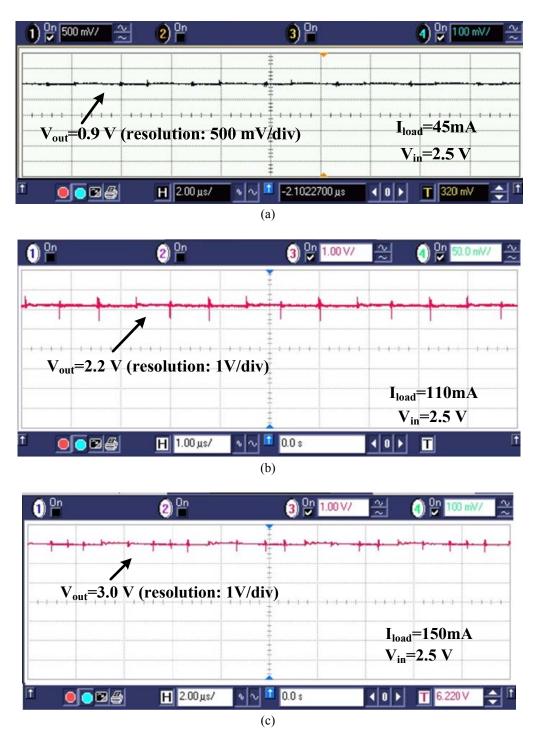

| Figure 4.4.3 Steady-state $V_{out}$ at (a) 0.9 V for step-down conversion, (b) 2.2 V for s | tep-down  |

| conversion, and (c) 3.0 V for step-up conversion.                                          | 111       |

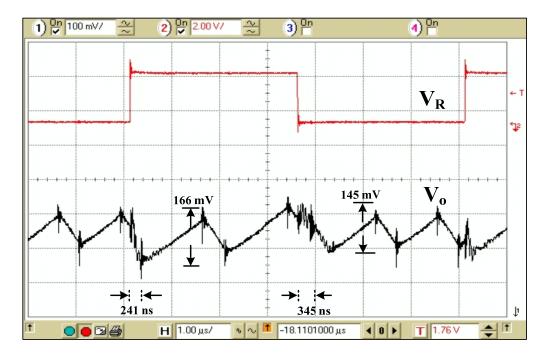

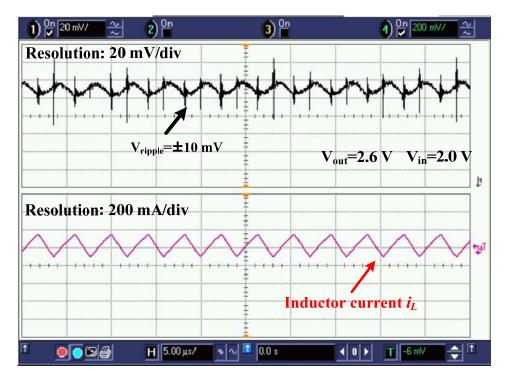

| Figure 4.4.4 Measured output ripple voltage (upper) and inductor current $i_L$ (lower)     | 112       |

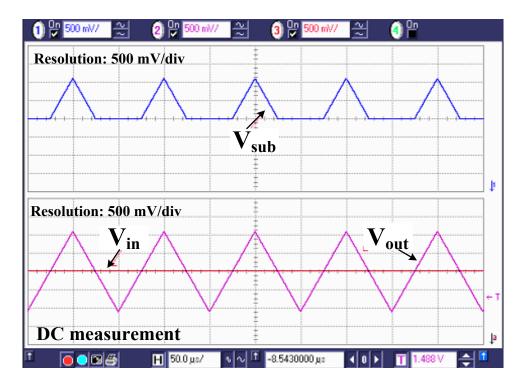

| Figure 4.4.5 Measured DC performance of the ASSC.                                          | 112       |

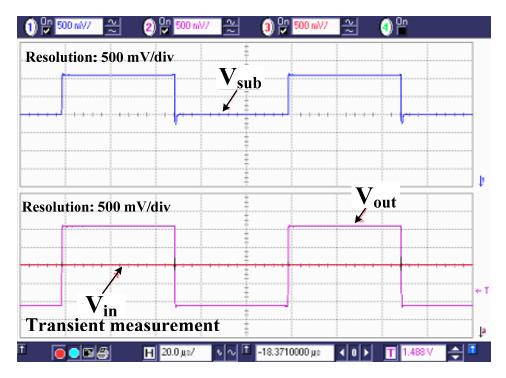

| Figure 4.4.6 Measured transient performance of the ASSC.                                   | 113       |

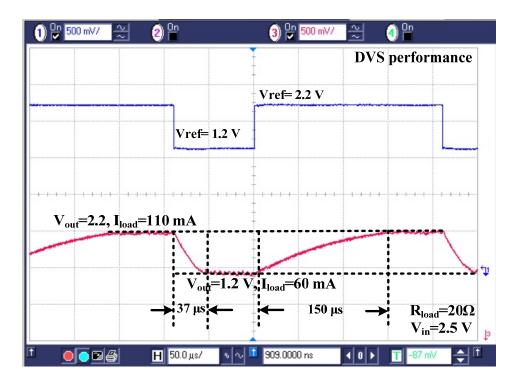

| Figure 4.4.7 Measured dynamic performance for DVS: (upper) $V_{ref}$ steps down from 2.2   | to 1.2 V, |

| (lower) measured $V_{out}$                                                                 | 114       |

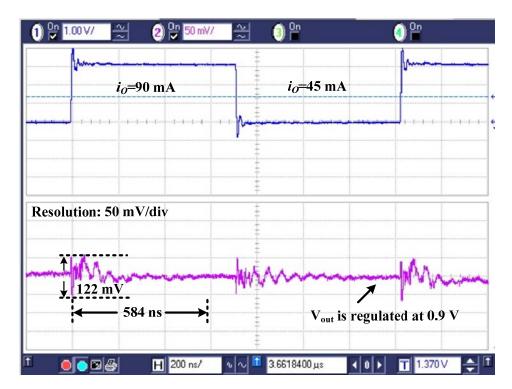

| Figure 4.4.8 Measured load transient response: (upper) load current $i_O$ steps up a       | nd down   |

| between 45 and 90 mA, (lower) measured output voltage $V_{out}$ .                          | 114       |

| Figure 5.2.1 System block diagram of the proposed design.                                  | 120       |

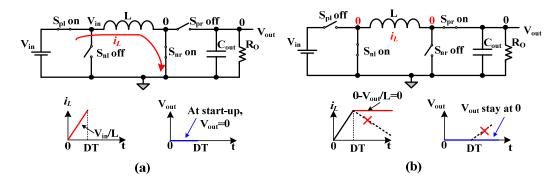

| Figure 5.2.2 Start-up issue in a step-up/down converter: (a) State 1, and (b) State 2      | 122       |

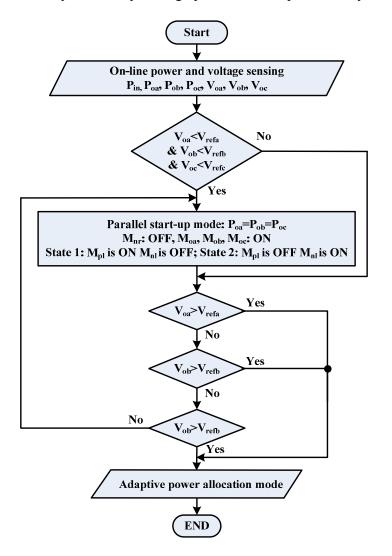

| Figure 5.2.3 Flow chart of the parallel start-up control scheme.                           | 123       |

| Figure 5.2.4 Timing diagram of the parallel start-up scheme.                               | 124       |

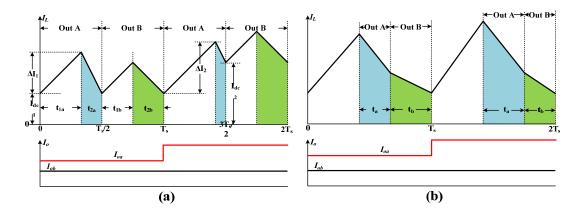

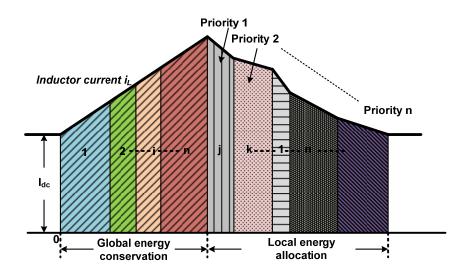

| Figure 5.2.5 Inductor current at light load mode.                                          | 125       |

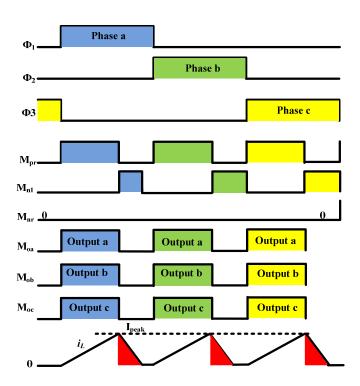

| Figure 5.2.6 Timing diagram at heavy load mode.                                            | 126       |

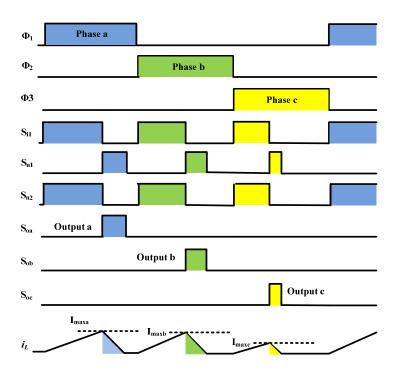

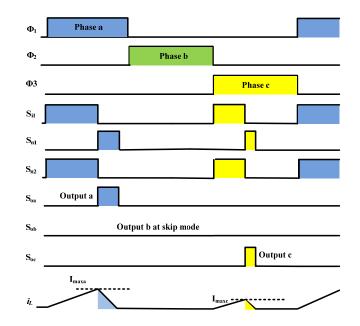

| Figure 5.2.7 Timing diagram at unbalanced power demand mode                                | 126       |

| Figure 5.3.1 Schematic of the process and temperature independent ring oscillator base     | ed ADC.   |

|                                                                                            | 127       |

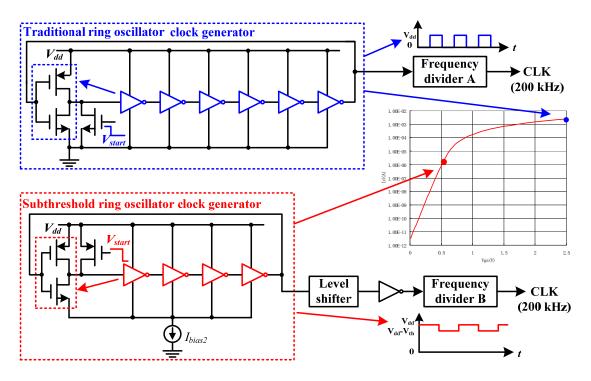

| Figure 5.3.2 Traditional and the proposed ring oscillator clock generators.                | 128       |

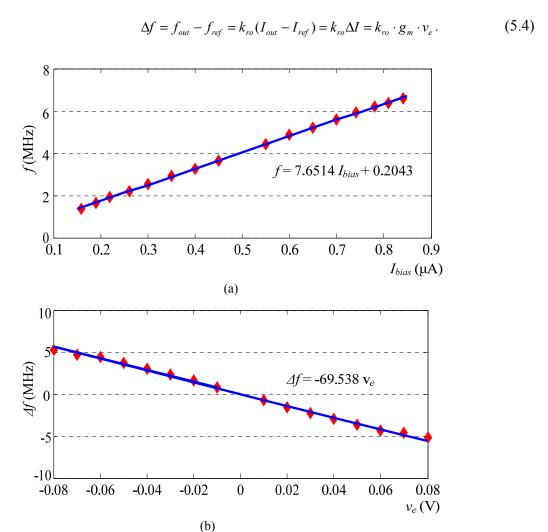

| Figure 5.3.3 Simulation results of the sub-threshold ring oscillator: (a) frequency-biasir | g current |

| dependency, and (b) frequency-voltage error dependency.                                    | 129       |

| Figure 5.3.4 Schematic of a power sensor.                                                  | 130       |

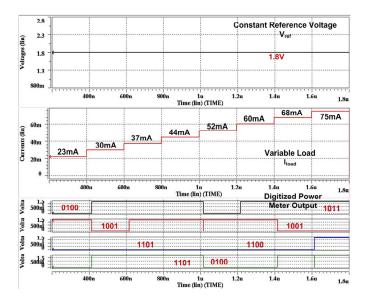

| Figure 5.3.5 Simulated digital power sensing and processing technique outputs: with        | constant  |

| reference voltage V <sub>ref</sub> .                                                       | 132       |

| Figure 5.3.6 Simulated digital power sensing and processing technique outputs: with        | constant  |

| load current I <sub>load</sub> .                                                           | 133       |

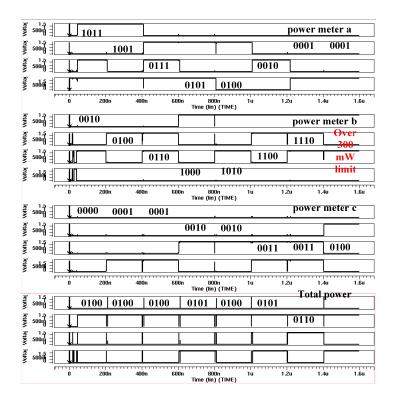

| Figure 5.3.7 Simulated digital power sensing and processing technique outputs: total po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | wer  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| demand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 133  |

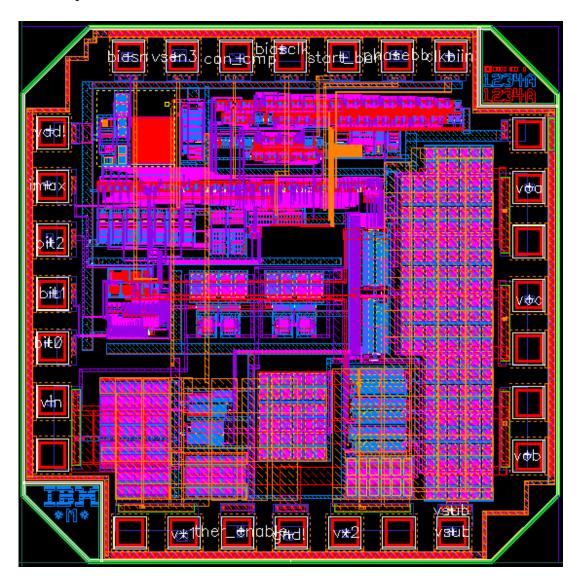

| Figure 5.4. 1 Chip layout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 134  |

| Figure 5.4.2 Simulated steady-state three output voltages (top), and inductor current $i_L$ (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | om). |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 135  |

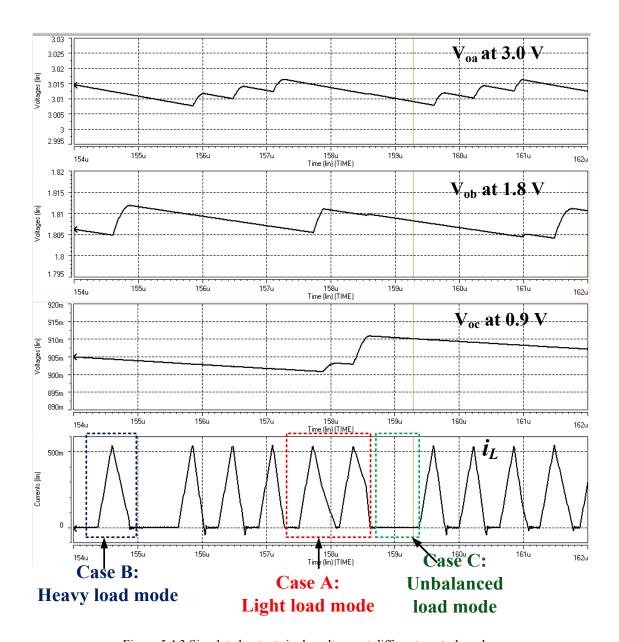

| Figure 5.4.3 Simulated output ripple voltages at different control modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 136  |

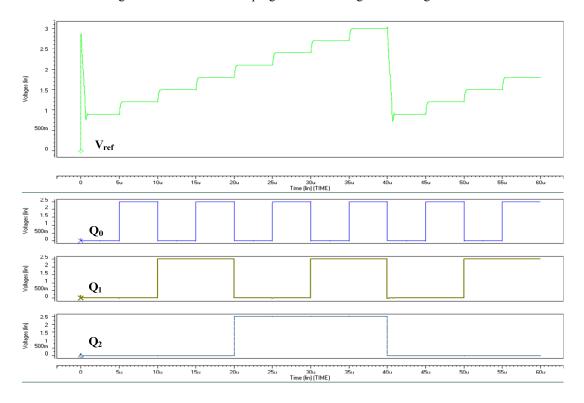

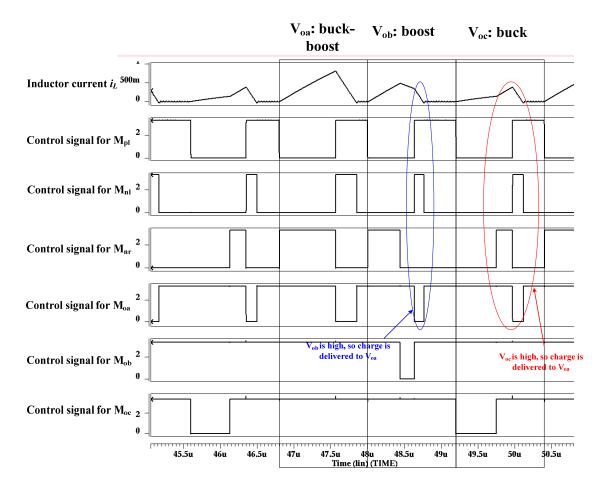

| Figure 5.4.4 Simulated control signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 137  |

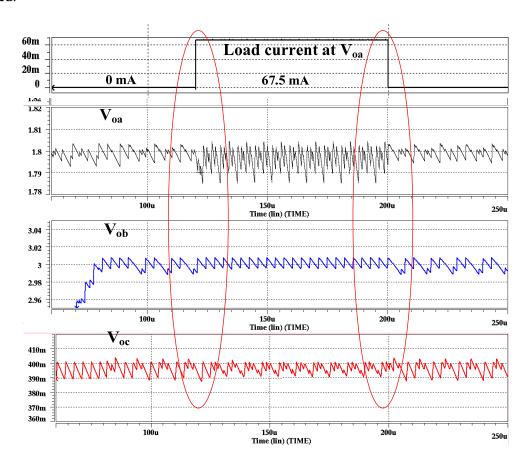

| Figure 5.4.5 Load transient performance test.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 138  |

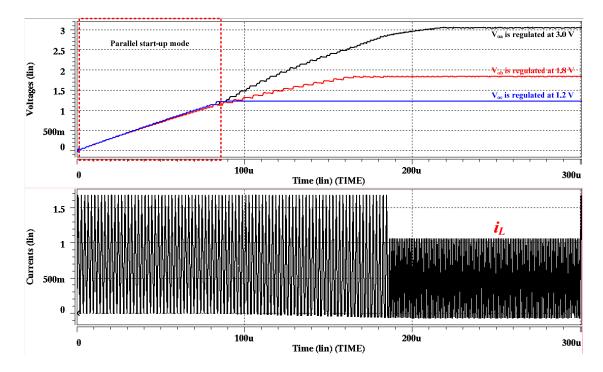

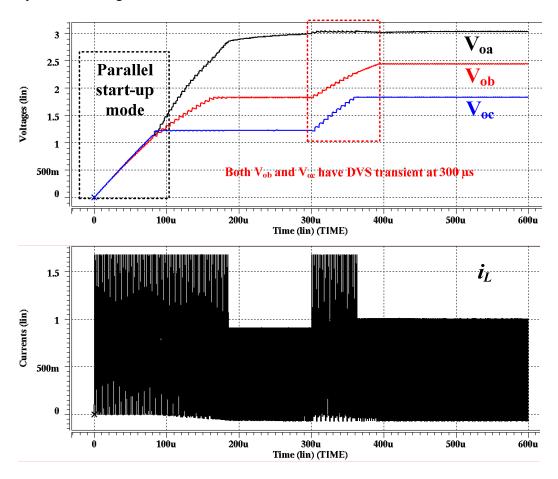

| Figure 5.4.6 Start-up and DVS transient performance test.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 139  |

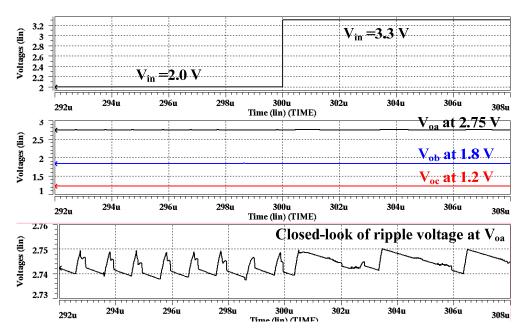

| Figure 5.4.7 Line regulation performance test: $V_{in}$ (top), regulated outputs (middle), and a cleaning state of the contraction of the contrac | ose- |

| up view at Voa(bottom).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140  |

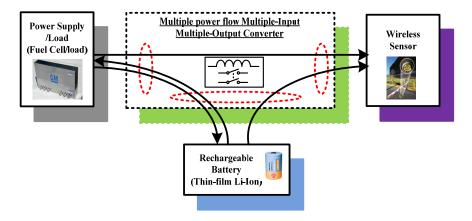

| Figure 6.3.1 A multiple input multiple output system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 143  |

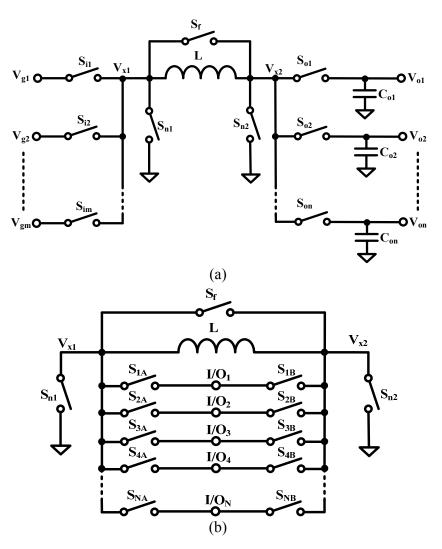

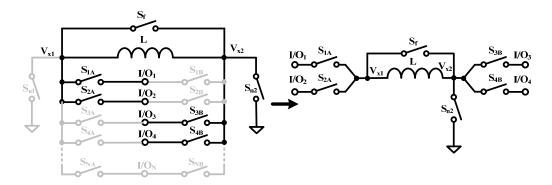

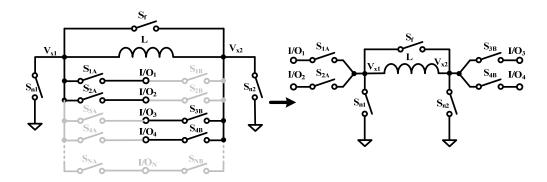

| Figure 6.3.2 (a) the proposed step-up/down SIMIMO converter, and (b) a generic topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 144  |

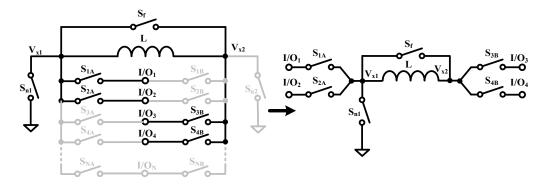

| Figure 6.3.3 Extension of the proposed SI-MOMO converter power stage: achieving SI-DIDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )    |

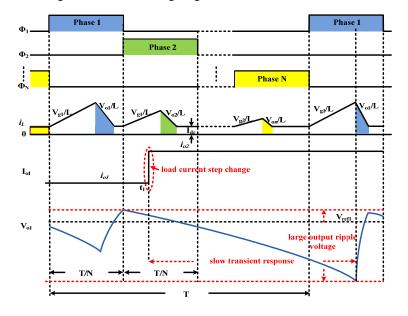

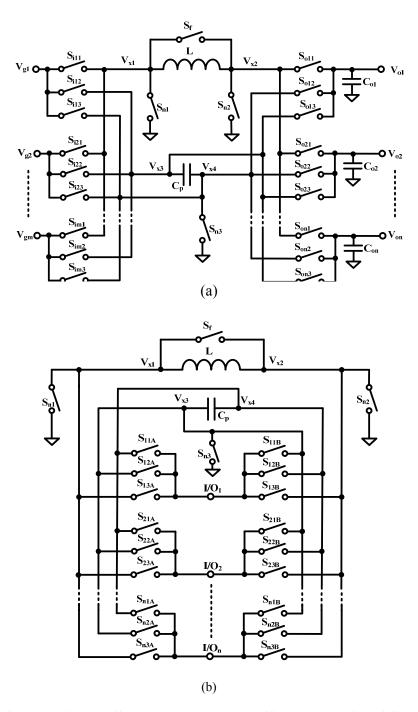

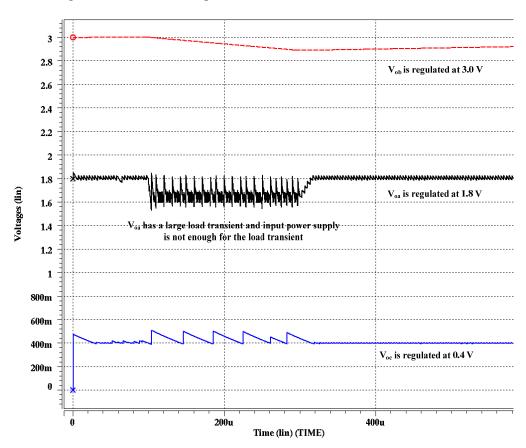

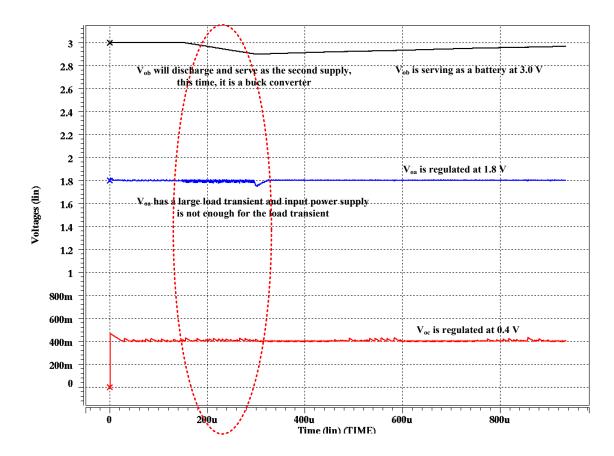

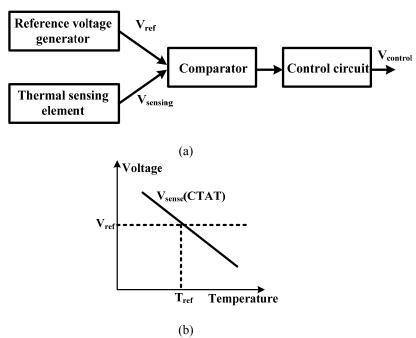

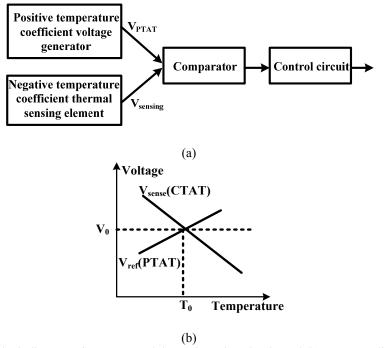

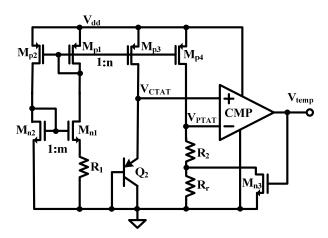

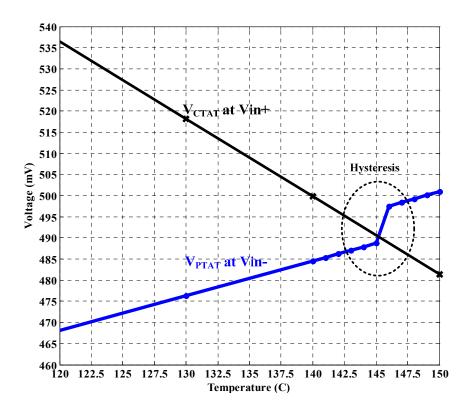

| buck converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 145  |