# DEVELOPING A HIGHLY PARALLELIZED TCR SYNTHESIS ALGORITHM ON GPGPU AND FPGA FOR ACCELERATING THE STUDY OF IMMUNE SYSTEMS

by

Elnaz Tavakoli Yazdi

Copyright © Elnaz Tavakoli Yazdi 2018

A Dissertation Submitted to the Faculty of the

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

In Partial Fulfillment of the Requirements

For the Degree of

MASTER OF SCIENCE

In the Graduate College

THE UNIVERSITY OF ARIZONA

# THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE

As members of the Master's Committee, we certify that we have read the thesis prepared by *Elnaz Tavakoli Yazdi*, titled *Developing a highly parallelized TCR synthesis algorithm on GPGPU and FPGA for accelerating the study of immune systems* and recommend that it be accepted as fulfilling the thesis requirement for the Master's Degree.

Ali Akoglu

adali

Tosiron/Adegbija

Salim Hariri

Date: ///4/2018

Date: 11/14/2018

Date: /2/12/2018

Date: 12/10/2018

Final approval and acceptance of this thesis is contingent upon the candidate's submission of the final copies of the thesis to the Graduate College.

I hereby certify that I have read this thesis prepared under my direction and recommend that it be accepted as fulfilling the Master's requirement.

Ali Akoglu,

Associate Professor,

Electrical and Computer Engineering Department

University of Arizona

#### ACKNOWLEDGEMENTS

I would like to thank all the people who stood by my side during my masters studies. First of all, I would like to express my gratitude to my advisor. I am very thankful to Prof. Ali Akoglu for his advice, guidance, comments, and support during this path. Without him, this work would never have been accomplished. I have learnt a lot from him during past two years and his teachings will be always appreciated throughout my career.

I would like to thank Dr.Adam Buntzman who helped me with understanding the medical aspect of the DNA recombination process.

I would like to thank my beloved husband (Mohsen Bahrami) who has been very patient, supportive, helpful, and understanding throughout this path. Without his supports, it would be almost impossible to start this path. Last but not least, I would like to express my gratitude to my parents who has been very supportive during past two years.

# DEDICATION

$I\ dedicated\ this\ work\ to\ my\ family...$

# TABLE OF CONTENTS

| LIST O | F FIGU | JRES                                                      | 7              |

|--------|--------|-----------------------------------------------------------|----------------|

| LIST O | F TAB  | LES                                                       | 8              |

| ABSTR  | ACT    |                                                           | 9              |

| CHAPT  | TER 1  | INTRODUCTION                                              | 11             |

| CHAPT  | TER 2  | The DNA Recombination Algorithm                           | 16             |

|        | 2.0.1  | Biological Perspective                                    | 16             |

|        | 2.0.2  | Algorithmic Perspective                                   | 18             |

|        | 2.0.3  | Input data set                                            | 19             |

| CHAPT  | TER 3  | The GPU-based Implementation of DNA Recombination         |                |

|        |        |                                                           | 21             |

| 3.1    |        | arallelization Strategy                                   | $\frac{1}{21}$ |

| 3.2    |        | Sit-Wise Implementation                                   | 23             |

|        | 3.2.1  | Conversion of input data set                              | $\frac{1}{24}$ |

|        | 3.2.2  | GPU Kernel                                                | $\frac{1}{25}$ |

| 3.3    | •      | Inditi-GPU Implementation                                 | 29             |

| 3.4    |        | imental Setup                                             | 30             |

| 3.5    |        | imental Results                                           | 31             |

| 3.3    | 3.5.1  | Thread Block Configuration Analysis                       | 31             |

|        | 3.5.2  | Bit-wise Simulation Results                               | 34             |

|        | 3.5.3  | Multi-GPU Simulation Results                              | 34             |

| CHAPT  | TER 4  | FPGA-based Implementation of The DNA Recombination        |                |

|        |        | · · · · · · · · · · · · · · · · · · ·                     | 40             |

| 4.1    | Hardw  | vare Implementation of N Level Parallelization            | 40             |

|        | 4.1.1  | N Level Parallelization Strategy                          | 41             |

|        | 4.1.2  | Processing Unit                                           | 43             |

|        | 4.1.3  | n-sequence Initiator Unit                                 | 46             |

|        | 4.1.4  | In vivo Address Generator Unit                            | 47             |

|        | 4.1.5  | Processing Element                                        | 48             |

|        | 4.1.6  | Address Generator Unit                                    | 49             |

| 4.2    | Simula | ation Results of the N Level Parallelization Architecture | 49             |

| 4.3    |        | oacks of N Level Parallelization Architecture             | 50             |

| 4.4    |        | vare Implementation of VJ Level Parallelization           | 52             |

|        |        | VI Level Parallelization Strategy                         | 52             |

# ${\bf TABLE\ OF\ CONTENTS}-Continued$

|         | 4.4.2  | Combination Unit                                           | 56 |

|---------|--------|------------------------------------------------------------|----|

|         | 4.4.3  | Comparison Unit                                            | 58 |

|         | 4.4.4  | First In First Out Buffer (FIFO)                           | 62 |

| 4.5     | Simula | ation Results of the VJ Level Parallelization Architecture | 64 |

| 4.6     | Drawb  | oack of VJ-Level Parallelization architecture              | 64 |

| 4.7     | Hashir | ng Functions                                               | 67 |

|         | 4.7.1  | The class of function $H_3$                                | 68 |

| 4.8     | Hardw  | vare Implementation of VJ-Level Parallelization Using      |    |

|         | Hash l | Function                                                   | 68 |

|         | 4.8.1  | Combination Unit                                           | 69 |

|         | 4.8.2  | Hash Unit                                                  | 69 |

|         | 4.8.3  | Comparison Unit                                            | 69 |

| 4.9     | Simula | ation Results of the VJ Level Parallelization Architecture |    |

|         | Using  | Hash Function                                              | 70 |

| СНАРТ   | TER 5  | Conclusion and Future Work                                 | 74 |

| 5.1     | Conclu | asions                                                     | 74 |

| 5.2     | Future | e Work                                                     | 75 |

| Referen | ces    |                                                            | 77 |

# LIST OF FIGURES

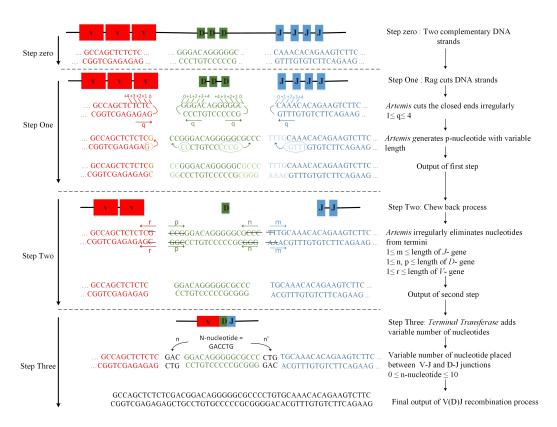

| 2.1 | Brief view of the $V(D)J$ recombination process. The figure shows p-nucleotide formation with length one for $V-$ gene termini, two for left side of $D-$ gene termini, four for right side of $D-$ gene termini and four for $J-$ gene termini in step one. Example depicts elimination of one nucleotide on the $V-$ gene termini, three nucleotides on both side of the $D-$ gene and two nucleotides on $J-$ gene termini | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

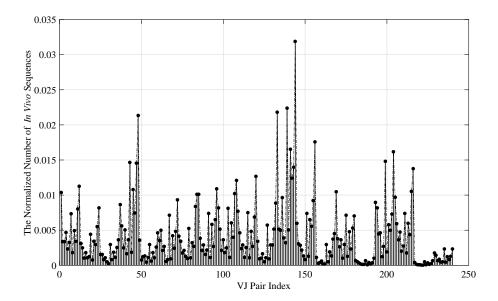

| 3.1 | A Normalized distribution of <i>in vivo</i> sequences across 240 VJ pairs                                                                                                                                                                                                                                                                                                                                                     | 23 |

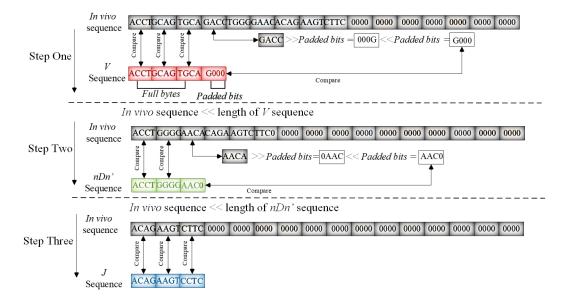

| 3.2 | Brief view of the comparison process for the bit-wise version of $V(D)J$ recombination process                                                                                                                                                                                                                                                                                                                                | 28 |

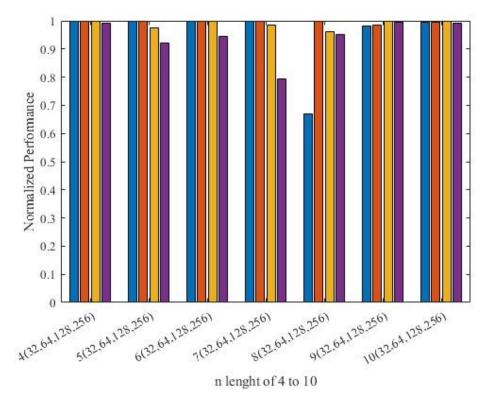

| 3.3 | Normalized results of four different thread per block configura-<br>tions (32, 64, 128, 256) for n-nucleotide length of four to nine.                                                                                                                                                                                                                                                                                         |    |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                               | 32 |

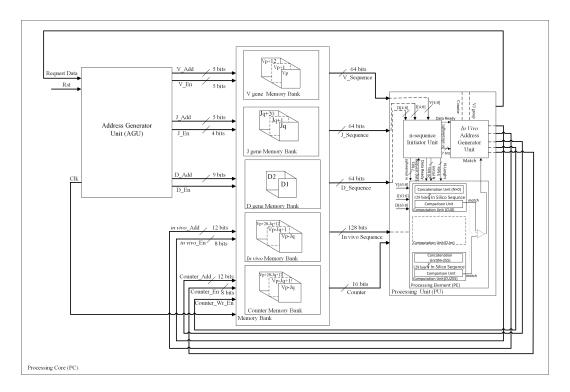

| 4.1 | The hardware implementation of $V(D)J$ recombination process using the N-level parallelization approach                                                                                                                                                                                                                                                                                                                       | 42 |

| 4.2 | The resource utilization of the proposed architecture for different values of the $D_P$                                                                                                                                                                                                                                                                                                                                       | 45 |

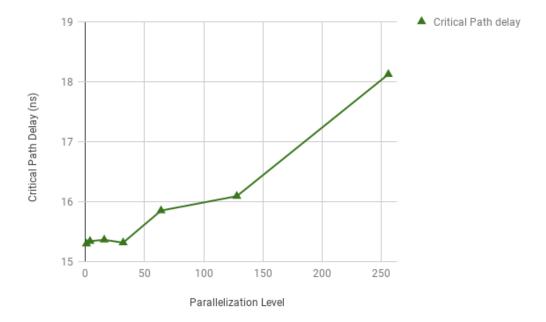

| 4.3 | The critical path delay of the proposed architecture for different values of the $D_P$                                                                                                                                                                                                                                                                                                                                        | 45 |

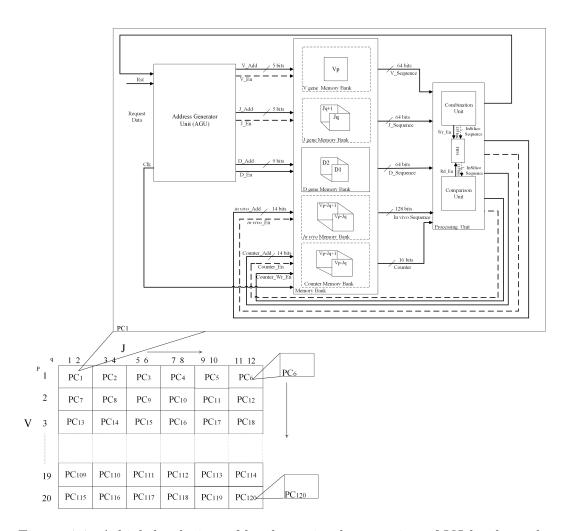

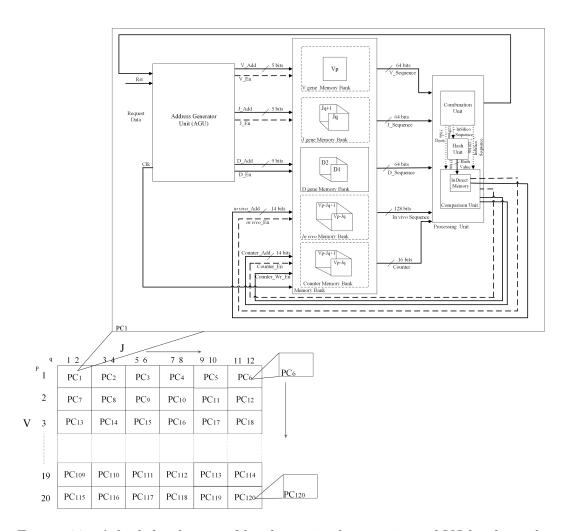

| 4.4 | A high level view of hardware implementation of VJ level par-                                                                                                                                                                                                                                                                                                                                                                 |    |

| 4.5 | allelization for the $V(D)J$ recombination process The algorithmic description for the structure of Combination                                                                                                                                                                                                                                                                                                               | 55 |

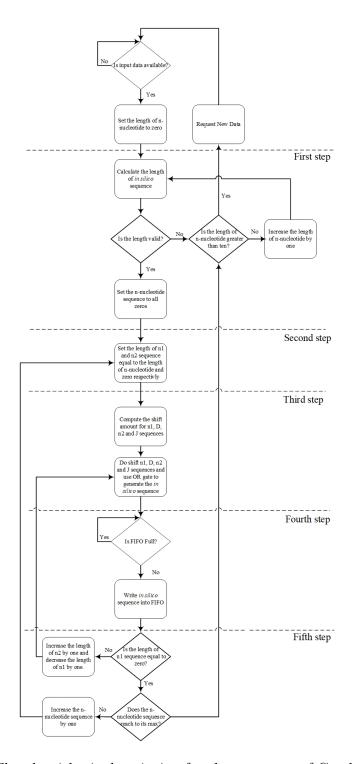

|     | unit                                                                                                                                                                                                                                                                                                                                                                                                                          | 59 |

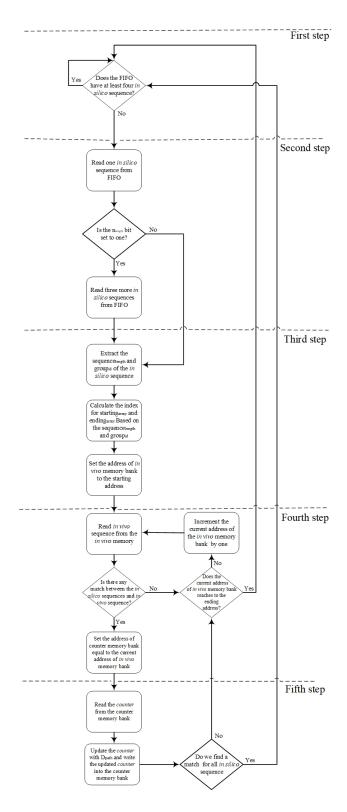

| 4.6 | The algorithmic description for the structure of Comparison unit.                                                                                                                                                                                                                                                                                                                                                             | 63 |

| 4.7 | A high level view of hardware implementation of VJ level par-                                                                                                                                                                                                                                                                                                                                                                 |    |

|     | allelization with hash unit for the $V(D)J$ recombination process.                                                                                                                                                                                                                                                                                                                                                            | 71 |

# LIST OF TABLES

| 3.1  | The total number of unique n-nucleotide sequences based on the        |    |

|------|-----------------------------------------------------------------------|----|

|      | length of n-nucleotide                                                | 24 |

| 3.2  | 2-bit encoding scheme                                                 | 25 |

| 3.3  | P100 GPU Streaming Multiprocessor Resources                           | 30 |

| 3.4  | GPU resource utilization for n-nucleotide length of seven with        |    |

|      | four different thread block configurations                            | 33 |

| 3.5  | The memory footprint for the bit-wise implementation in com-          |    |

|      | parison with the baseline approach                                    | 35 |

| 3.6  | Execution time on single GPU: Baseline vs. Bit-wise Imple-            |    |

|      | mentations                                                            | 35 |

| 3.7  | Execution Time for the bit-wise implementation on different           |    |

|      | number of GPUs                                                        | 36 |

|      |                                                                       |    |

| 4.1  | The total number of unique n-nucleotide sequences and total           |    |

|      | number of possible combinations of $n_1Dn_2$ with a given $D$ se-     |    |

|      | quence based on the length of n-nucleotide                            | 44 |

| 4.2  | Resource Utilization for a single CU                                  | 44 |

| 4.3  | FPGA Resource Utilization for the N Level Parallelization Ar-         |    |

|      | chitecture                                                            | 51 |

| 4.4  | Execution time for the FPGA and bit-wise GPU-based imple-             |    |

|      | mentations using Virtex-7 and P100 GPU, respectively                  | 52 |

| 4.5  | Resource Utilization for a single PU                                  | 53 |

| 4.6  | The total number of <i>in silico</i> sequences with the same features |    |

|      | for a given n-nucleotide's length with and without the $D$ gene.      | 61 |

| 4.7  | Execution time for the n-level and VJ level parallelization ap-       |    |

|      | proach for FPGA-based implementation using Virtex-7 in com-           |    |

|      | parison with the bit-wise GPU-based implementations using P100.       | 65 |

| 4.8  | FPGA Resource Utilization for the VJ Level Parallelization Ar-        |    |

|      | chitecture                                                            | 66 |

| 4.9  | Execution time for the VJ level parallelization approach with         |    |

|      | and without hash function for FPGA-based implementation us-           |    |

|      | ing Virtex-7 in comparison with the bit-wise GPU-based imple-         |    |

|      | mentations using P100                                                 | 72 |

| 4.10 | FPGA Resource Utilization for the VJ Level Parallelization Ar-        |    |

|      | chitecture Using Hash Function                                        | 73 |

#### ABSTRACT

The V(D)J recombination process is the primary mechanism for generating a diverse repertoire of T-cell receptors (TCRs) essential to the adaptive immune system for recognizing a wide variety of diseases. The diverse set of TCR are required by the immune system to increase the chance of accurate identification of the foreign invaders, which results in successful recovery from diseases. Furthermore, analysis of the TCR repertoire helps immunologists to understand the functionality of immune system in presence of different diseases and find the correlation between diseases and immune receptors. However, modeling this diverse TCR repertoire is computationally challenging as the total number of TCRs to be generated and processed can exceed  $10^{18}$  sequences. This massive scale of data processing poses as the barrier for immunologists to successfully understand the functionality of human immune system. Therefore, reducing the timescale of modeling the TCR repertoire will help immunologists to test their assumptions and solve their fundamental questions.

In this study, we propose FPGA and GPU-based implementation of V(D)J recombination process for accelerating the analysis of TCR repertoire. For the GPU-based implementation, we propose a bit-wise implementation of the V(D)J recombination algorithm, which reduces the memory footprint and the execution time by factors of 4 and 2 respectively compared to the current state-of-the-art GPU-based implementation. We devise an encoding procedure to convert the input data set from character based domain to binary domain and pack a sequence of four characters into a single byte for the bitwise implementation. We also proposed new indexing scheme for addressing input data that are not aligned with the byte-addressing. We present a multi-GPU implementation, experimentally identify suitable workload partitioning strategies for both single- and multi-GPU implementations, and finally expose the relationship between workload size and limited scalability offered by the

algorithm on a cluster with up to eight GPUs. We show that the bit-wise implementation reduces the execution time from a time scale of 40.5 hours to 18.9 hours on a single GPU and to 4.3 hours on a 8-GPU configuration.

For the FPGA-based implementation, we first utilize the N-level parallelization approach that is used for the GPU-based implementation. Simulation results show that this approach does not perform as expected for the FPGA-based implementation of V(D)J recombination process due to the communication overhead between FPGA components. Therefore, we propose the VJ level parallelization approach to reduce the communication among components. We show that the VJ-level architecture reduces the execution time by a factor of 2.34 in comparison with the N-level parallelization approach.

#### CHAPTER 1

#### INTRODUCTION

Adaptive immune system protects vertebrates by detecting and neutralizing foreign invaders (antigens) using T-cell receptors (TCRs), which are placed on the surface of a T-cell [1]. A T cell is a sub-type of white blood cell that plays a central role in recognizing and neutralizing fragments of antigen with the TCRs. A TCR recognizes an antigen by detecting the small protein fragments that are on the surface of that antigen, and then sends a massage to the nucleus of its T-cell. This successful recognition induces a response for eliminating antigens [2]. The diversity in the TCR pool increases the chance of detecting a variety of antigens for the adaptive immune system, which is the first step of a successful recovery from diseases. Analysis of TCR pool (repertoire) is crucial for understanding the functionality of healthy immune system, determining the nature of successful and unsuccessful immune responses, and understanding the immune mechanism in presence of different diseases such as type I diabetes, various cancers (blood, breast, colorectal, etc.), rheumatoid arthritis (autoimmune disease), and multiple sclerosis [3]. The response of immune system to specific antigen often leaves evidence in the form of repertoire sequence patterns (signatures) that are common across individuals and these signature patterns can be associated with the corresponding antigen. Identification of these signatures help biologists to understand the correlation between the immune receptors and different disease, which provides researchers with the ability to identify immune receptor clones that can be converted into precision vaccines [4–6].

A diverse set of TCRs is required for the adaptive immune system to successfully detect wide variety of antigens. This diversity is achieved by the immune systems of the vertebrates through the DNA recombination process, which is known as the V(D)J recombination [7]. This process involves rearrangement of variable (V), diversity (D), and joining (J) gene segments in a combinatorial way chosen from members of each gene family [7,8]. The form and length of each gene segment varies across different species, and it is more complex in the human than vertebrates. For example, there are 20 different V genes in the mice, while there are 50 different V genes in human [9].

In the clinical environment, ability to predict the repercussion of immune system to different antigens is a challenging research problem [9–13]. For such prediction capability, immunome researchers need a way to model all possible unique TCR sequences (TCR repertoire) that can be generated through the recombination process. This would allow the researchers count the number of times each unique sequence is created through different recombination paths, which forms the baseline for statistical analysis on correlating a specific TCR chain with a specific antigen. However, modeling of all  $\alpha\beta$ TCR sequences is considerably complex, since the potential TCR repertoire of mouse contains more than  $10^{15}$  sequences [14]. Furthermore, the total number of paths exhausted to generate all the sequences is expected to exceed  $10^{18}$ . This massive scale of data processing poses as the barrier for immunologists, which has led them to computationally tractable statistical methods [15], [16] with a trade off in accuracy [15], [16]. Reducing the timescale of modeling all TCR $\beta$  chains will enable immunologists to test the validity of their assumptions and solve their fundamental questions rapidly such as: What is the real size of the  $TCR\beta$ repertoire? Is the procedure of generating TCRs random or biased? What can we say about the frequency distribution of various TCR sequences? The most exhaustive study on TCR synthesis to this date [17] models more than  $10^{14}$  $TCR\beta$  chains by exploiting the data parallel nature of the recombination process and mapping the algorithm entirely on a single graphic processor unit (GPU). This study shows that the execution time can be scaled down to 13 days using an NVIDIA GTX 480 from 52 weeks on a single general purpose processor. This is the first study that models all the potential  $TCR\beta$  repertoire of the mouse in which the number of recombination pathways exceeds  $4 \times 10^{14}$ .

For the human system, diversity of the TCR repertoire shows variations from one person to another and increases significantly such that there are more than 50 million TCRs in the immune system of 100 humans. From mouse data set to human data set, the scale of the data increases from  $10^5$  to  $10^7$ . Furthermore, in humans there are 50 basic V genes, 2 basic D genes, and 13 basic J genes, while in the mouse data set there are 20 V genes, 2 basic D genes, and 12 J genes. From mouse to human, the TCR repertoire increases by three orders of magnitude to  $10^{18}$  [17]. To be able to cope with the scale of the simulations at  $10^{18}$  level, our aim in this study is to investigate ways to reduce the execution time and memory footprint of the recombination process so that we can rapidly model systems that are more complex than the mouse. For this, we make the following contributions:

- Devising a bit-wise GPU-based implementation of the recombination process, which consists of fine-grained shift, concatenation, comparison, and counting over the binary domain input data set.

- Extending the bit-wise implementation to a multi-GPU environment and evenly distributing workload across the GPUs being used.

- Utilizing the N-level parallelization approach that is used for the GPU-based implementation and implementing the V(D)J recombination algorithm on the field programmable gate array (FPGA).

- Devising a VJ-level parallelization method for the FPGA-based implementation to overcome the draw back of N-level parallelization method.

In order to utilize the bit-wise operations, we devise an encoding procedure to convert the input data set from character based domain to binary domain (2-bits per character) and pack a sequence of 4 characters into a single byte. The bit-wise representation of input data set reduces memory access time by a factor of 4, since we can fetch four characters with one memory access. After mapping the input data set to binary domain, we pad the end of input data sequences whose length are not divisible by eight with 0's. Correspondingly, we develop a new indexing scheme for addressing the input data stored in the constant memory of GPU to avoid using padded bits of the input data that are not aligned with the byte addressing. Then, we introduce a task

generation function that generates a unique task for each thread based on its identification number, ensures a unique path for a given sequence by each thread and eliminates the communication between the GPU threads. The two-bit based representation reduces the global and constant memory footprint by factors of 4 and 3.5 compared to the baseline GPU implementation [17]. Utilizing bit-wise operations and reducing the amount of data transfers reduces the execution time by a factor of 2 using an NVIDIA Tesla P100 GPU. CUDA natively supports 32-bit integer shift and 32-bit bitwise "AND", "OR", and "XOR" operations [18], which allows us to implement the bit-wise version of recombination process as it heavily relies on shift, concatenation (using "shift" and "or") and comparison ("xor") operations.

For the multi-GPU implementation, we define an *indexing* function, which generates global index for threads in different GPUs based on the index of GPU, and the GPU dimension. Then, we use the proposed *task generation* function to generate unique tasks for each GPU thread. Overall, our aim is to count number of times each *in vivo* sequence can be generated artificially by rearranging input data set (V, D, J) genes and n-nucleotide sequence) to model the TCR repertoire. Therefore, each thread works on its assigned task based on its global index, repeatedly generates a unique sequence, increments the counter for that sequence if it exists in the *in vivo* data set till that thread completes the task of generating all possible sequence based on its given n-nucleotide. The multi-GPU implementation reduces the execution time from a scale of 18.9 hours to 4.3 hours using 8 GPUs.

As stated above, the recombination process involves intensive amount of fine-grained shift, concatenation, comparison, and counting operations over a data-set generated on the fly. We take advantage of the fine grained parallelism offered by the FPGA whose architecture naturally matches the program architecture of the recombination process. Therefore, we first map the V(D)J recombination algorithm onto the target FPGA using the GPU-based parallelization approach, which is known as N-level method. In order to address this, we first define the degree of parallelism for the final hardware architecture. We also show the relation between degree of parallelism with critical path delay

and resource utilization. We form the memory hierarchy based on the selected degree of parallelism and design required components to map the recombination process. In addition, we utilize the length and VJ pair index of the generated sequence to pare down the comparison search space. Experimental results for the FPGA implementation show that the N-level parallelization approach causes communication overhead among FPGA components and result in poor performance. Therefore, we devise a VJ-level parallelization approach to form a unique memory hierarchy to match the data access patterns for various stages of the algorithm, which results in the elimination of communication overhead among components. We show that the VJ-level parallelization approach accelerate the recombination process by a factor of 2.34 in comparison with the N-level method for the FPGA-based implementation.

The rest of this dissertation is organized as follows: Chapter 2 provides an overview of the DNA recombination algorithm from biological and algorithmic perspectives. Chapter 3 describes a bit-wise implementation of the recombination process on a single and multi-GPU. A detailed explanation of the FPGA-based implementation of the V(D)J recombination process is provided in Chapter 4. Conclusions and future work are discussed in Chapter 5.

#### CHAPTER 2

### The DNA Recombination Algorithm

The V(D)J recombination process is a specialized DNA rearrangement critical to the adaptive immune system. In this section, we describe the DNA recombination process from biological and algorithmic perspectives, and highlight key features related to our parallelization approach. We also provide detailed explanation about the structure of input data set used in our experiments.

# 2.0.1 Biological Perspective

The TCRs are created by recombination of the V, D, and J gene segments. Fig. 2.1 illustrates the recombination process using an example sequence formed by the V, D and J segments. The two rows in step 0 represent the two complementary DNA strands: the template strand and its mirror image the coding strand. As the V, D, and J segments go through the recombination process for generating unique sequences in search of a sequence that matches the antigen, diverse set of sequences are generated. There are three critical steps that contribute to this diversity, which we summarize by highlighting the core factors in the following paragraphs.

In the first step, the recombination activation gene, recombinase, cuts the DNA at the joints between V and D segment pairs, and D and J segment pairs. Immediately, the template strand and coding strand bind to each other where the cut occurs. Subsequently, the Artemis exonuclease enzyme releases circular ends irregularly to generate a palindromic nucleotide (p-nucleotide) with variable lengths [7, 19, 20]. From the starting point of the arrow shown in step one of Fig. 2.1, up to length of four genes from the coding strand are appended to the template strand on its right termini for the V segment, both termini for the D segment, and left termini for the J segment. This p-nucleotide addition of length up to four is one of the major contributors to the diversity during the recombination process.

Figure 2.1: Brief view of the V(D)J recombination process. The figure shows p-nucleotide formation with length one for V- gene termini, two for left side of D- gene termini, four for right side of D- gene termini and four for J- gene termini in step one. Example depicts elimination of one nucleotide on the V- gene termini, three nucleotides on both side of the D- gene and two nucleotides on J- gene termini.

In the second step, both strands of the V, D and J segments go through a process called chewback. Once more, the  $Artemis\ exonuclease$  enzyme is involved in this chewback process, in which a variable number of nucleotide are eliminated from the V, D and J termini. The chewback is applied from right to left on the V segment, left to right on the J segment, and from both directions on the D segment. The amount of chewback ranges from one nucleotide to the length of that gene segment, which is the second contributor to the diversity.

In the third step, the Terminal Transferase (TDT) enzyme catalyzes the addition of n-nucleotides between V-D and D-J gene pairs. We consider the size n ranging between zero and ten. This range has been proven to regenerate 99.5% of the sequences in our  $in\ vivo$  data-set [17]. The  $in\ vivo$  data set has been built based on the samples that were sequenced on the Roche FLX 454 platform at the UNC-Chapel Hill High Throughput Genome Sequencing Core. The  $in\ vivo$  data set consists of 101,822 functional sequences. Finally, the DNA ligase IV closes off the V and D termini to form V-D junction, and D and D termini to form D-D junction. Compared to the first two factors that contribute to the diversity, having n-nucleotide addition between V-D and D-D junctions enormously grow the combinational search space, and acts as the main contributor of the diversity.

#### 2.0.2 Algorithmic Perspective

We refer to the V(D)J recombination as VnDn'J recombination in this discussion about the algorithmic perspective. In this case, V, D, and J indicate the unique sequences from each set of corresponding segments while 'n' indicates the set of all possible nucleotide combinations. We refer the generated VnDn'J sequences as the ' $in\ silico$ ' sequences. Thus, to generate the  $in\ silico$  sequences, we need four inputs: V, D, J, and the n-nucleotide (n) sequences.

There are four bases: A, G, C, T, used to generate a n-nucleotide sequences. Thus, for n-nucleotide length m, there are  $4^m$  unique combinations. In the recombination process, these n-nucleotide sequences can be attached on either side or on both sides of the D sequence. To differentiate between the positions,

**Algorithm 1:** Pseudo code for V(D)J Recombination Algorithm : V, J, D and n - nucleotide sequences Input Output : Number of times each unique in vivo sequence is generated (Counter) 1 for i = 0 to number of V sequences do for j = 0 to number of J sequences do 2 for k = 0 to number of D sequences do 3 for m = 0 to number of n - nucleotide sequences do 4 Combination =CombineString(V[i], n[m], D[k], n[m], J[j]); for  $p = n - nucleotide_{lenght}$  to 0 do 5  $\text{move } (N[m][p] \rightarrow T[n-nucleotide_{lenght}-p])$ for n = 0 to number of in vivo sequences do 6 if Combination == invivo[n] then Counter[n] = Counter[n] + 1;

we define the n-nucleotides as n and n'. The D sequence can cut the n-nucleotide at any position. Therefore, this complex junctional combination may lead to generation of an identical sequence through numerous ways. Our main purpose is to count the number of unique pathways that generate a given  $in\ vivo$  sequence through the recombination process. Algorithm 1 shows the pseudo code for the VnDn'J recombination process with nested loops that iterate through each V, D, J and n sequence to form  $in\ silico$  sequences. All single sequences are combined and stored in the variable Combination through the nested loops. If a generated sequence is found in the current  $in\ vivo$  set, we increment the counter value for that sequence. This process continues until the entire combinational search space is exhausted.

#### 2.0.3 Input data set

The input data sets consist of V, D, J and  $in\ vivo$  genes. In C57BL/6 mice, there are 20 basic  $V\beta$  genes, 2  $D\beta$  genes and 12 basic  $J\beta$  genes. However, all possible patterns such as chewback and palindromic forms for each of the functional V, D and J gene sequences need to participate in the recombina-

tion process for modeling the TCR repertoire as illustrated in Fig. 2.1. For example, the first basic V gene has a length of 14. For the V gene, up to four genes can be appended to the right end of the V gene from its mirror strand (step one, indicated as +4, +3, +2, +1), therefore the actual length of this gene can be up to 18. This would result with 18 different sequences based on the chewback process (step two). D and J gene data sets go through similar process as explained in Section 2.0.1, therefore each V, D and J gene data set consists of several forms of sequences with different lengths. Each V, D, J, and in vivo sequence is generated using four bases (A, G, T, and C). In C57BL/6 mice, the *in vivo* data set involves 101,822 sequences, which are grouped based on the specific VJ pair used to generate that sequence. There is no other recombination path for an in vivo sequence other than the specific VJ pair, which generates that specific sequence. This is a key feature that we can exploit to reduce a search space within the in vivo data set and reduce the execution time. There are 240 such pairs since we have 20 basic V genes and 12 basic J genes in mice.

#### CHAPTER 3

The GPU-based Implementation of DNA Recombination Algorithm

We provide a detailed description regarding the GPU-based implementation of the DNA recombination algorithm in this chapter. We first evaluate two parallelization approaches for GPU-based implementation, and select the most suitable method based on their advantages and disadvantages in Section 3.1. In Section 3.2, we propose the bit-wise GPU-based implementation for the DNA recombination algorithm. We extend the bit-wise implementation to a multi-GPU environment and provide a detailed explanation in Section 3.3. Finally, we explain the experimental setup and simulation results for bit-wise implementation on a single and multi-GPU in Section 3.3 and 3.5, respectively.

### 3.1 The Parallelization Strategy

In this section, we analyze two parallelization approaches for the GPU-based implementation of V(D)J recombination process. For each strategy, we attempt to answer the following questions: 1) What would be the workload distribution based on the parallelization strategy? 2) Does the proposed parallelization strategy result in an even workload distribution among the threads?

Since each V-J pair generates a specific sequence, the first parallelization approach would be the V-J level parallelism by assigning one V gene, one J gene, and both D genes to each thread to perform the recombination process. In this assignment, each thread needs to cover all possible n-nucleotide lengths (zero to ten) along with all possible combinations of four bases for any given n-nucleotide lengths. However, as there are  $20\ V$  genes and  $12\ J$  genes, this implementation would require only 240 threads and result with significantly low thread utilization on the GPU. A finer granularity of V-J level parallelism can be realized by assigning one form (refer to chewback and palindromic forms of each input gene) of V gene, one form of J gene, and both D genes to each

thread. For this approach, the total number of required threads is 102,446 since there are  $362\ V$  genes,  $283\ J$  genes in the chewback and palindromic forms for the mice data set. This finer level of parallelization occupies 90% of the threads on the target P100 series GPU.

In order to answer the second question for the fine-grained V-J level parallelization approach, we need to consider workload for both combination and comparison steps. We refer to the combination step as a process of generating all possible in silico sequences for a given input data and the comparison step as a process of comparing generated sequences with in vivo sequences. The workload distribution for combination step is even since, each thread is assigned one form of V gene, one form of J gene, and both D genes. In order to evaluate the workload distribution for the comparison step, we provide a normalized distribution of in vivo sequences across 240 VJ pairs in Fig. 3.1. As shown, total number of in vivo sequences is not evenly distributed across different VJ pairs, which directly affects the workload of each thread. Since, each thread needs to compare its generated in silico sequences against every in vivo sequence in the corresponding VJ pair, the fine-grained V-J based assignment results in an uneven workload distribution among GPU threads.

The second solution would be n-nucleotide level parallelism, where each thread is assigned a unique n-nucleotide sequence and the recombination process is applied on that unique sequence. In this assignment, the workload for the *combination* step is even since, each thread works on one n-nucleotide sequence. In addition, the workload distribution for *comparison* step is equal among GPU threads, since GPU threads are working on the same V and J gene. Therefore, total number of *in vivo* sequence for the comparison process are equal among active threads. Since all threads share the same V and J gene pairs, this approach can take advantage of the shared memory to improve the the memory bandwidth utilization.

In order to decide which one of the stated approaches performs better in terms of execution time, we evaluate the workload per thread for the *combination* step, in both approaches. In the fine-grained V-J level parallelism, each thread generates in silico sequences for all possible forms of n-nuclotide

Figure 3.1: A Normalized distribution of *in vivo* sequences across 240 VJ pairs.

for length of zero to ten. Table 3.1 shows the total number of n-nucleotide sequence based on the length. Therefore, a single thread must generate 706,042,015 in silico sequences through the entire process as there are 1,381,717 unique n-nucleotide sequence in total and there are 505 sequences for D gene. In the n-nucleotide based assignment, each thread generates 51,735,230 in silico sequences since there are 362 V genes, 283 J genes, and 505 D genes. As a result, workload per thread in fine-grained V-J level parallelism is almost 13 times higher than n-nucleotide parallelization approach. In the following sections we present our approach to bit-wise and multi-GPU implementations based on n-nucleotide level parallelism.

#### 3.2 The Bit-Wise Implementation

Mainly, there are two phases for the implementation of bit-wise representation. The first phase involves converting the input data set from character domain to binary domain, which we refer to as data conversion phase. The second phase consists of developing GPU kernel using bit-wise operations. We provide detailed explanation regarding the implementation of bit-wise version of the

Table 3.1: The total number of unique n-nucleotide sequences based on the length of n-nucleotide

| $N_{-}len$ | Total number of unique           |

|------------|----------------------------------|

|            | $n	ext{-}nucleotide \ sequences$ |

| 0          | 1                                |

| 1          | 4                                |

| 2          | 16                               |

| 3          | 64                               |

| 4          | 256                              |

| 5          | 1,024                            |

| 6          | 4,096                            |

| 7          | 16,384                           |

| 8          | 65,536                           |

| 9          | 262,144                          |

| 10         | 1,048,576                        |

| Total      | 1,381,717                        |

recombination process in the following subsections.

### 3.2.1 Conversion of input data set

The main objective of using bit-wise operations for mapping the recombination process is to reduce the memory footprint and execution time. We represent each base (A, C, T, and G) with two bits as shown in Table 3.2 and pack a sequence of four bases into a single byte. For those sequences (V, D, and J) whose length is not divisible by four, remainder bases will not fill the byte to its capacity. In this case, we zero pad the end of sequence such that the length of the binary string is divisible by eight (one byte). Let's consider a V sequence, which has the length of ten characters (20 bits). For this case, four zeros are appended to the end of V sequence. As a result, the new V sequence has 24 bits, which requires three bytes of data to store in the memory. The last byte of this V sequence has four zero padded bits, which we refer to as V padded bits. We call the first two bytes, which only contain the original bits

| $Gene\ base$ | 2-bit representation |

|--------------|----------------------|

| A            | 00                   |

| T            | 01                   |

| С            | 10                   |

11

Table 3.2: 2-bit encoding scheme

of the V sequence as  $full\ byte$ .

G

The maximum length of *in vivo* sequences is 60 characters (bytes). In the baseline implementation, *in vivo* sequences are padded with 0's so that the length of all sequences are equal to 64 bytes. This guarantees that the allocation of each sequence is equal to the number of threads in two warps, ensuring the memory is aligned to realize coalesced memory accesses. In the binary representation form with 2 bits per base (character), we also follow the same encoding procedure with padding, and represent each *in vivo* sequence with fixed size of 16 bytes.

In the baseline implementation, all possible forms of V, D, and J sequences are stored in the constant memory to take advantage of the temporal locality it offers. However, the *in vivo* sequences are stored into the GPU's global memory as there are too many *in vivo* sequences (>  $10^5$ ) to fit into the constant memory. For the bit-wise implementation, the *in vivo* data set is also stored in the global memory since the required constant memory for the binary representation of *in vivo* data set is larger than the available constant memory in a target GPU.

#### 3.2.2 GPU Kernel

For the n-nucleotide level parallelism, the total number of threads is set to the total possible combinations for a given n-nucleotide sequence  $(4^m)$ , where m is the length of n-nucleotide sequence. In this case, all active threads can fetch the same input data  $(V, D, J, \text{ and } in \ vivo)$  and each thread can apply the recombination process over its assigned n-nucleotide. This reduces the number

**Algorithm 2:** Pseudo code for the *task generator* function which generate a unique n-nucleotide sequence for each thread based on its thread and block indexes.

```

Input : threadId, blockId, and blockDim

Output : n-nucleotide sequence

base[4] = {00, 01, 10, 11}

G_{index} = threadIdx.x + blockIdx.x * blockDim.x

for i = 0 to 3 do

| for j = 0 to 9 increment by 2 do

| temp = base [{G_{index} + G_{index}/4^{4*i+(j-2/2)}}%4] \ll (8 - j)

| n-nucleotide[i] |= temp

```

of memory accesses (global and constant) for a specific gene sequence to one among all active threads.

As mentioned earlier, the *in vivo* sequences are partitioned into 240 groups based on the V and J gene used to generate these sequences. This feature was used to pare down the comparison search space in [17]. Indeed, *in silico* sequences are only compared against the corresponding portion of the *in vivo* data set instead of being compared with the entire data set. We also use this feature in our design. Therefore, our GPU kernel starts its execution by using V and J gene indexes to determine how many and which *in vivo* sequence will be used for the recombination process. Then each thread is assigned a unique n-nucleotide sequence based on the length of n sequence, thread ID, and block ID. We propose a function that generates a unique binary n-nucleotide sequence for each thread to guarantee that there is no duplicate n-nucleotide sequence. Algorithm 3 shows the pseudo code for the task generator function, which is used to generate a unique binary n-nucleotide sequence. After assigning a unique task to each GPU thread, the recombination process starts on the GPU.

There are four main loops in the GPU kernel. The first for loop iterates through each in vivo sequence. Upon entering this loop, threads within the block read a single in vivo sequence from the global memory into the shared

memory. Since, the *in vivo* sequence is shared among all threads within a block, we use *synchthread()* to assure that all threads wait until the memory transaction is completed.

The second for loop iterates through each V sequence in the current V gene set. All threads within a block read the same V sequence from the constant memory, while they work on a different n-nucleotide sequence. We compare the V sequence against the *in vivo* sequence. To accomplish this, we calculate the total number of full bytes and padded bits for a given V sequence. Then, we iterate through each full byte of the V sequence, and compare it with in vivo sequence one byte at a time. If there is a mismatch, we terminate the current comparison for all threads and read a new in vivo sequence from global memory. Otherwise, we continue on to comparing the last byte of V sequence with the pertinent byte of in vivo sequence. In order to accomplish this, we shift the corresponding byte of in vivo sequence to the right by the total number of padded bits. Accordingly, we shift that byte to the left by the same amount. We will refer to this process as an alignment process. Finally, we compare the last byte of V sequence with the aligned byte of in vivo sequence. This procedure is shown in step one of Fig. 3.2. If the V sequence completely matches with the *in vivo* sequence, we proceed to the next loop. Otherwise, we read a new *in vivo* sequence and repeat the process.

The third loop iterates through each D sequence. There is a difference between this loop (D-loop) and the previous loop (V-loop). The D sequence can cut the n-nulceotide sequence at any position as explained in Chapter 2. Therefore, each thread generates all possible combinations of nDn' sequence for a given D and n-nucleotide sequences. Then, they compare their nDn' sequence with  $in\ vivo$  sequence from the last character that was found to be identical to the V sequence in the previous loop. This is accomplished by shifting the  $in\ vivo$  sequence to the left by the length of V sequence. The comparison procedure is shown in step two of Fig. 3.2, and it is the same process as explained in the V-loop. If there is a mismatch between the  $in\ silico$  and  $in\ vivo$  sequence, then the thread terminates the current comparison, generates a new combination for nDn' sequence, and repeats the process.

Otherwise, we continue on to the next loop. It should be noted that, if a thread generates all possible forms of nDn' sequence for a given D and n sequence, then we load new D sequence and repeat the process.

The final loop iterates through each J sequence. In this loop, we first calculate the length of VnDn'J sequence and compare it with the length of in vivo sequence. If the length of in silico and in vivo sequences are not equal, then we terminate the current comparison and load a new J sequence. Otherwise, we compare the J sequence with the latter portion of in vivo sequence as shown in step three of Fig. 3.2. If a sequence generated by a thread matches with the in vivo sequence, then that thread increments the local counter stored in a register. A thread may generate the targeted in vivo sequence through multiple recombination paths. After all threads complete their n-nucleotide level workload, the counter value stored in the shared memory for that in vivo sequence is updated through reduction. At the end of this loop, reduction determines the total number of times an in vivo sequence is generated artificially. Finally, the first thread within the block updates the counter value in the global memory.

Figure 3.2: Brief view of the comparison process for the bit-wise version of V(D)J recombination process.

### 3.3 The Multi-GPU Implementation

In n-nucleotide level parallelization, threads of a GPU are assigned a unique n-nucleotide sequence while they work on the same V and J gene. From multi-GPU implementation perspective, in order to generate a unique n-nucleotide sequence for each active thread, we define a global index for each thread based on its thread Id, block Id, GPU Id, and GPU dimension as shown in (3.1) and utilize a task generator function that is presented in the algorithm 3.

$$G_{index} = threadIdx + blockIdx \times blockDim + GPUIdx \times GPUDim.$$

(3.1)

For the n-nucleotide based parallelization approach, GPU threads work on the same VJ pair so they require accessing the same  $in\ vivo$  sequences. Therefore, we replicate input data set and store it in the constant and global memories of each GPU to avoid data transfer between the GPUs.

In order to distribute the workload among GPUs, we first calculate the total number of required threads, which is  $4^m$ , where m is the length of n-nucleotide sequence. Then, we calculate the total number of required blocks based on the thread-block configuration (refer to Fig. 3.3). Finally, we calculate total number of blocks in each GPU using 3.2. For example, we need 262, 144 (4<sup>9</sup>) threads for n-nucleotide length of 9. As we will present later in the experimental results, 128 threads per block configuration, which requires 2048 blocks in total is the desired configuration on a single GPU. Assuming that we have two GPUs, based on 3.2, each GPU is assigned 1024 blocks with 128 threads in each block. In this assignment, the workload distribution among GPUs and GPU threads are equal.

$$\#blocks = \frac{\#total\ threads - 1}{\#threads\ per\ block \times \#GPUs + 1}$$

(3.2)

In order to obtain the final result from multiple GPUs, we perform a reduction process [21]. This process accumulates all the results in the root node and copy them to global memory of the host.

Table 3.3: P100 GPU Streaming Multiprocessor Resources

| Parameter                         | Value |

|-----------------------------------|-------|

| Compute Capability                | 6.0   |

| Streaming Multiprocessors (SM)    | 56    |

| Threads per Warp                  | 32    |

| Maximum Thread Block Size         | 1024  |

| Maximum Thread Blocks per SM      | 32    |

| Maximum Warps per SM              | 64    |

| Maximum Threads per SM            | 2048  |

| Maximum 32-bit Registers per SM   | 65536 |

| Maximum Registers per Block       | 65536 |

| Maximum Registers per Thread      | 255   |

| Maximum Shared Memory Size per SM | 64 KB |

| Constant Memory Size              | 64 KB |

#### 3.4 Experimental Setup

We conducted our experiments on a cluster consisting of NVIDIA P100 GPU accelerators. The system is composed of 400 nodes (Intel Haswell V3 28 core processor, 192 GB RAM per node) in which 46 of them are configured as accelerator nodes with a single Nvidia P100 GPU in each node. The cluster uses FDR Infiniband for node to node interconnect and 10 Gb Ethernet for node to storage interconnect. Table 3.3 summarizes the GPU parameters. The P100 GPU has 56 streaming multiprocessors (SM), each limited to having up to 2048 threads, 32 thread blocks, and 64 KB shared memory [22]. For the bit-wise implementation of the V(D)J recombination algorithm with n-level granularity, each thread utilizes 48 registers, while there are 65536 registers available per SM. Therefore, the maximum number of active threads per SM is 1365 due to the register usage constraint. Also, it should be noted that the shared memory usage is not the limiting factor for the active threads per SM. As discussed in Section 3.2, the shared memory usage per block is 16 bytes plus one byte per thread for the counter value storage. Thus if we consider block size of 128 threads, only 134 bytes of shared memory is required per thread block, allowing 489 thread blocks per SM. Given that for n-nucleotide length of nine, there are 2048 blocks for the 128 threads per block configuration. Due to register usage constraint, there are only 10 active thread blocks per SM. As a result, we do not reach the limiting factor (489 thread blocks per SM) for the shared memory usage.

### 3.5 Experimental Results

We start our analysis by determining the best thread-block configuration for different n-nucleotide lengths on a single GPU. We then compare the execution time of our bit-wise based implementation with the baseline [17] implementation for each n-nucleotide length. Finally, we present execution time analysis for the multi-GPU implementation with up to eight nodes.

# 3.5.1 Thread Block Configuration Analysis

Fig. 3.3 shows the normalized results for four different thread block configurations over n-nucleotide length ranging from four to ten. For each length of n-nucleotide sequence, we take the shortest execution time and use that as a dividing factor over the execution time of other configurations. Therefore, normalized value of 1 represents the best performance for a given length. We did not consider n-nucleotide length of zero to three as there are not sufficient threads to utilize multiple warps executing concurrently. As shown in Fig. 3.3, there are negligible differences between performance of various thread block configurations for length of four to six since, there are not sufficient tasks to utilize all the available multiprocessors of the P100 GPU. For n-nucleotide length of less than seven, the thread utilization is bellow 14% as the total number of required threads is less than 2<sup>14</sup> while there are 114,688 threads available in P100. However, for n-nucleotide length of greater than seven, the workload increases such that more than 60% of available GPU threads are used. There is a 20% reduction in the performance for the n-nucleotide length of seven based on 256 threads per block configuration compared to other configurations. For n-nucleotide length of seven, the recombination pro-

Figure 3.3: Normalized results of four different thread per block configurations (32, 64, 128, 256) for n-nucleotide length of four to nine.

cess completes in one iteration for every thread per block configuration since the total number of required threads is  $4^7 = 16,384$ , which is less than the total number of available threads in a single P100 GPU. The lower thread block utilization per SM is the root cause for this performance loss as shown in Table 3.4, which reports the thread, thread block, and *warp* utilization for each configuration.

We observe a 35% reduction in the performance for the n-nucleotide length of eight, if 32 threads per block are employed. The reason is that the maximum number of active thread-blocks per multiprocessor is 32 in the P100 GPU. Therefore, we are limited by the hardware to have 32 active blocks per SM in which each block has 32 threads. As a result, we have  $2^{10} \times 56$  active threads in GPU while we need  $2^{16}$  threads to complete the recombination process in one iteration. Let's consider the 64 threads per block configuration, based on the register constraint usage, we can have maximum 1365 active threads per

| Table 3.4: GPU resource    | utilization for | n-nucleotide | length | of seven | with fo | ur |

|----------------------------|-----------------|--------------|--------|----------|---------|----|

| different thread block cor | ifigurations.   |              |        |          |         |    |

| thread block  | threads per SM | thread blocks | warp       |

|---------------|----------------|---------------|------------|

| configuration |                | per~SM        |            |

| 32            | 1024 (50%)     | 32 (100%)     | 32 (50%)   |

| 64            | 1344 (65%)     | 21 (65%)      | 42 (65%)   |

| 128           | 1280 (62.5%)   | 10 (31.25%)   | 40 (62.5%) |

| 256           | 1280 (62.5%)   | 5 (15.62%)    | 40 (62.5%) |

SM, and based on the thread block configuration, we can have maximum of 21 blocks with 64 threads. This results in total of  $21 \times 64 \times 56 = 75,264$  threads, which is greater than the required threads for n-nucleotide length of eight. Therefore, the recombination process completes in one iteration for thread block configuration of 64 for n-nucleotide length of eight, while it can not be completed in one iteration with 32 threads per block. We note that the difference between the performance of 64, 128, and 256 threads per block configurations is negligible with normalized values of 1, 0.961, and 0.95 respectively as the recombination process is completed in one iteration for all three configurations.

For n-nucleotide length of nine, the total number of required threads is  $4^9 = 262,144$ , which is greater than available threads in a single GPU. This will results in completing the recombination process in more than one iterations. For 64, 128 and 256 threads per block configurations, four iterations is required to complete the recombination process. As a result, there is a negligible difference between their performances with normalized values of 0.984, 1 and 0.994 respectively. However, the number of required iteration increases by one, if 32 threads are employed per block. Therefore, the poorest performance belongs to 32 thread per block configuration for n-nucleotide length of nine.

In summary, based on Fig. 3.3, we set thread block configuration to 64 for n-nucleotide lengths four to eight, 128 for lengths nine and ten. In the following subsection, we evaluate the performance of bit-wise and multi-GPU implementations with respect to the baseline implementation.

#### 3.5.2 Bit-wise Simulation Results

In order to evaluate the bit-wise implementation, we ran an experiment on a single Tesla P100 GPU using the baseline implementation. The timing analysis and memory footprint for this experiment are used as a reference point for performance comparison.

Table 3.5 shows the total amount of required memory for V, D, J genes, and in vivo data set using the bit-wise representation. As stated in table 3.5, the memory footprint for constant memory reduces by a factor of 3.4 compared to the baseline implementation, while the required global memory reduces by a factor of 4. Table 3.6 shows the execution time results for each n-nucleotide length. Last row shows the total execution time for the recombination process. As shown, the total execution time reduces by a factor of 2.1 in comparison with the baseline implementation. For both implementations, after n-nucleotide of eight, the execution time increases by about a factor of four at each increments of n-nucleotide length by one. For n-nucleotide length of eight, we utilize 87.5% of available SM on a single GPU since 49 MPs with thread block configuration of 64 (smallest execution time) are used. Therefore, increasing the workload beyond this point directly results in increasing the execution time. The workload per GPU depends on the total number of unique n-nucleotide sequence as mentioned in 3.1. Therefore, increasing the length of n-nucloetide by one results in increasing the total number of unique n-nucleotide sequences by a factor of four and as a result execution time increases with the same factor.

#### 3.5.3 Multi-GPU Simulation Results

Table 3.7 shows the execution time of the multi-GPU version of the bit-wise implementation for each n-nucleotide length. We ran experiments by using up to eight GPUs to evaluate the trends in execution time improvement with respect to change in number of GPUs.

The key observation from Table 3.7 is that there is slight increase in execution time if multiple GPUs are utilized for n-nucleotide length less than

Table 3.5: The memory footprint for the bit-wise implementation in comparison with the baseline approach.

|         |               |          | Percentage |

|---------|---------------|----------|------------|

| Gene    | Baseline [17] | Bit-wise | reduction  |

| V       | 1448          | 425      | 70.65      |

| J       | 3107          | 913      | 70.61      |

| D       | 3210          | 908      | 71.71      |

| in vivo | 6517568       | 1629392  | 75.00      |

Table 3.6: Execution time on single GPU: Baseline vs. Bit-wise Implementations

| N length | Baseline (min) | Bit-wise (min) |

|----------|----------------|----------------|

| 0        | 8.36           | 8.68           |

| 1        | 10.17          | 9.34           |

| 2        | 12.57          | 10.14          |

| 3        | 15.38          | 10.92          |

| 4        | 18.47          | 11.74          |

| 5        | 21.73          | 12.56          |

| 6        | 25.67          | 13.69          |

| 7        | 32.09          | 16.23          |

| 8        | 102.03         | 49.82          |

| 9        | 426.9          | 196.76         |

| 10       | 1755.35        | 797.8          |

| Total    | 2428.7         | 1137.7         |

eight. The reason behind this observation is the fact that the P100 GPU is over-provisioned; the total number of required threads for any n-nucleotide length less than eight are less than the maximum  $2048 \times 56 = 57,344$ ) active threads. Moreover, the extra reduction step for a multi-GPU implementation becomes a slight overhead.

However, for n-nucleotide length more than seven, we observe a reduction in the execution time with multiple GPUs. This is due to the fact that a single GPU is almost fully utilized at 87.5% as explained in Section 3.5.1 for

| er of GPUs.                                                                            | $8\text{-}GPUs\ (min)$                                                                                                                                   | 60.6 | 9.78 | 10.56 | 11.35 | 12.12 | 12.97 | 13.88 | 15.23 | 17.52 | 28.70  | 116.22 | 257.42 |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|

|                                                                                        | $7\text{-}GPUs \; (min)$                                                                                                                                 | 9.1  | 9.78 | 10.55 | 11.35 | 12.13 | 13.01 | 13.89 | 15.26 | 17.55 | 34.36  | 139.62 | 286.6  |

| different numc                                                                         | $(min) \mid 3\text{-}GPUs \; (min) \mid 4\text{-}GPUs \; (min) \mid 5\text{-}GPUs \; (min) \mid 6\text{-}GPUs \; (min) \mid 7\text{-}GPUs \; (min) \mid$ | 60.6 | 82.6 | 10.56 | 11.35 | 12.12 | 13.01 | 13.90 | 15.28 | 17.57 | 40.22  | 159.48 | 312.36 |

| Table 3.7: Execution 11me for the bit-wise implementation on different number of GPUs. | $5	ext{-}GPUs~(min)$                                                                                                                                     | 60.6 | 22.6 | 10.56 | 11.35 | 12.13 | 13.03 | 13.90 | 15.32 | 17.62 | 46.59  | 185.31 | 344.67 |

|                                                                                        | 4-GPUs $(min)$                                                                                                                                           | 60.6 | 22.6 | 10.55 | 11.34 | 12.12 | 13.03 | 13.91 | 15.43 | 18.92 | 58.60  | 231.37 | 404.13 |

|                                                                                        | $3\text{-}GPUs\ (min)$                                                                                                                                   | 9.28 | 26.6 | 10.75 | 11.55 | 12.37 | 13.24 | 14.39 | 15.66 | 22.77 | 82.00  | 301.18 | 513.16 |

|                                                                                        |                                                                                                                                                          | 9.23 | 9.91 | 10.69 | 11.48 | 12.29 | 13.18 | 14.34 | 16.61 | 27.89 | 112.86 | 455.73 | 694.21 |

|                                                                                        | $N \ length \mid 1\text{-}GPU \ (min) \mid 2\text{-}GPUs$                                                                                                | 8.68 | 9.34 | 10.14 | 10.92 | 11.74 | 12.56 | 13.69 | 16.23 | 49.82 | 196.76 | 8.762  | 1137.7 |

|                                                                                        | $N\ length$                                                                                                                                              | 0    | 1    | 2     | 3     | 4     | 2     | 9     | 7     | ∞     | 6      | 10     | Total  |

n-nucleotide length of more than seven. Since the required number of threads exceeds the active thread count per GPU, we observe the benefit of the multi-GPU implementation for n-nucleotide length eight and above. At this point, we expect to see relatively linear reduction in the execution time for a given n-nucleotide length as we increase the number GPUs. However, the simulation results show a saturating execution time trend where adding another GPU resource no longer helps reduce the execution time. We further investigate this behavior in the following paragraph.

For n-nucleotide length of nine, the required number of threads is  $4^9 = 262,144$ , which is more than the available threads in a single P100 GPU. Based on the register resource constraint, the recombination process can be completed in four iterations ( $\lceil (4^9/1280 \times 56) \rceil = 4$ ) using a single GPU. In this case there are 47,104 active threads in the last iteration utilizing 65% of the GPU threads. Employing two GPUs results in completing the process in two iterations, while there are 32,768 threads in the last iteration. In this case we are only utilizing 45% of the GPU threads. Therefore, we do not observe two times speed up with two GPUs. Utilizing four GPUs for n-nucleotide length of nine results with completing the process in one iteration. Beyond this point, increasing the number of GPUs causes under-utilization of each GPU and does not significantly improve the execution time.

For n-nucleotide length of ten, the required number of threads is  $4^{10} = 1,048,576$ . The recombination process is completed in 15 iterations ( $\lceil (4^{10}/1280 \times 56) \rceil = 15$ ) using a single GPU while there are 45056 active threads in the last iteration (62% GPU threads utilization). However, employing two GPUs results in completing the process in 8 iterations. The reduction of execution time from 797 minutes to 455 minutes is proportional to the reduction of iteration count from 15 to 8, which is the root cause for not observing a linear speedup with two GPUs. Using three GPUs results in completing the recombination process in 5 iterations while the GPU thread utilization is at 87.6% in the last iteration. When we employ four GPUs, iteration cont becomes 4. For the GPU count of five, six, and seven, the iteration count remains at 3 with fewer threads being utilized as the number of GPUs

increases. In order to complete the process in one iteration, we need to employ 16 GPUs. In overall, the saturation in the reduction of iteration count as we increase the GPU resources combined with the under utilization of the threads during the last iteration of the recombination process are the two root causes of saturating trend in execution time with respect to GPU count.

For the single GPU version, in the previous section, we showed that execution time increased by about a factor of four at each increments of the n-nucleotide length. Since we distribute the workload equally across the GPUs, we observe a similar trend for the multi-GPU implementation. For example, as shown in Table 3.7 execution time using two GPUs for n-nucleotide length of nine is about four times the execution time for n-nucleotide length of eight. Consistently we observe about a factor of four as we increase length from nine to ten for all GPU configurations.

Furthermore, we should expect the same execution time for two consecutive n-nucleotide lengths, while using one GPU for the first one and using four GPUs for the second one. As highlighted in Table 3.7, the execution time for n-nucleotide length of nine is 196 minutes by using single GPU. However we observe that execution time is 231 minutes for n-nucleotide of ten with four GPUs. We identify factors to this discrepancy as overhead of reduction process with the increase in number of GPUs, difference between the total number of nDn' combinations, and difference between the number of times each thread finds a match or terminates early. As stated earlier in Chapter 2, the D sequence can cut n-nucleotide sequence at any position, and each thread needs to generate all possible combinations of D with n-nucleotide sequence. As the length of n-nucleotide increases, the total possible combinations of nDn' increases by one for given D and n-nucleotide sequences. We note that an extra sequence needs to be combined with all possible forms of V and J gene sequences, which explains the difference between what we expected and what we observed. The difference in execution time reduces to around 9 minutes between n-nucleotide length eight with a single GPU and n-nucleotide length of nine with 4 GPUs. This discrepancy is about 2.6 minutes for the length pair of seven and eight with 1 and 4 GPUs respectively. We attribute this discrepancy reduction trend to the three factors listed above.

## CHAPTER 4

# FPGA-based Implementation of The DNA Recombination Algorithm

In this Chapter, we study the implementation of V(D)J recombination process on FPGA using the n-necleotide level parallelism that was used in the GPU-based implementation in Section 4.1. As we converge to a final hardware architecture, we provide a detailed explanation for each unit individually. We explain the experimental results for the n-level FPGA-based implementation of V(D)J recombination process in Section 4.2. Based on the simulation results, we explain the draw back of n-level parallelization method for FPGA-based implementation of the recombination process in Section 4.3. As a result, we proposed the VJ level parallelization approach for the FPGA-based implementation to overcome the draw back of n-level approach in Section 4.4. We describe the structure of each unit of the final hardware architecture for the VJ method. Finally, we describe the simulation results for the new parallelization approach in Section 4.5.

# 4.1 Hardware Implementation of N Level Parallelization

The goal for the hardware implementation of DNA recombination process is to accelerate the generation of all possible TCR sequences with any given V, D and J gene sequences and count the number of times each sequence can be generated artificially. As we converge to a final hardware architecture for this process we need to determine the level of parallelism and granularity of the processing elements for generating in silico sequences, orchestrate the data transfers between the memory and computation units, and balance the trade-off between throughput and resource usage. In this section, we first describe the parallelization strategy and then explain the structure of each unit that is used to implement the V(D)J recombination algorithm.

Fig 4.1 shows the proposed architecture for the hardware implementation

of the recombination process, which consists of three units, address generator unit (AGU), memory bank unit, and processing unit. The processing unit (PU) consists of processing element (PE), n-sequence initiator, and *in vivo* address generator units. The PE consists of a number of parallel computation units (CUs), which is formed of concatenation and comparison units.

The PU generates the number of times each in vivo sequence can be generated artificially in cooperation with the memory bank unit and corresponds to the inner most three loops in Algorithm 1. The n-sequence initiator provides the legitimate n-nucleotide length and reference n-nucleotide sequence for each CU based on the length of each input V, D and J gene sequences. Each CU generates a unique n-nucleotide sequence, forms all possible in silico sequences based on the input V, D and J gene sequences, and searches those generated sequences in the in vivo memory bank. The in vivo address generator unit allows reading the in vivo sequences and their counter values for each CU, and updates the counter value when a match is found by a CU. The AGU is corresponds to the outer most three for loops in Algorithm 1 in order to generate the indexes for accessing the V, D, J sequences. The memory bank unit is compromised of four sub-memory banks for maintaining input and output data sets.

# 4.1.1 N Level Parallelization Strategy

In this section, we present a series of experimental analysis to answer the following four questions that will help us determine the degree of parallelism  $(D_p)$  to realize in the final architecture: